部分使用外置SDRAM的STM32应用客户反映,在EMC测试中,由于SDRAM信号,其产品的辐射干扰超标。 终端PCB产品如果不能使用外壳屏蔽辐射干扰,往往需要通过修改SDRAM信号的PCB设计来解决此类问题。

下面就SDRAM的PCB应用设计中如何改善辐射干扰问题做一个概述,以供参考。

SDRAM设计中的辐射干扰对策

SDRAM 工作频率高,上升沿和下降沿都很陡。 因此在PCB设计中需要将其信号走线处理为高速信号传输线。 总的来说,应注意以下基本原则:

1.保持SDRAM信号完整性

SDRAM信号的失真会进一步展宽信号的辐射频谱,导致更严重的辐射问题。 因此,外包PCB设计时必须注意SDRAM信号的完整性设计。

建议使用四层或更多层板,将SDRAM信号的特性阻抗控制在50欧姆,尽量减少SDRAM总线上过孔的使用,保持阻抗连续性,减少阻抗不连续引起的信号反射;

SDRAM信号走线间距遵循3W原则,两个走线中心的间距尽量保持至少3倍线宽,这样可以减少信号间相互干扰造成的信号失真;

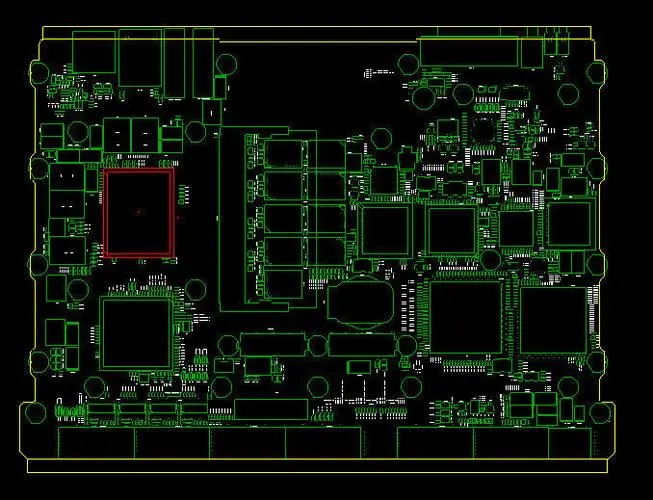

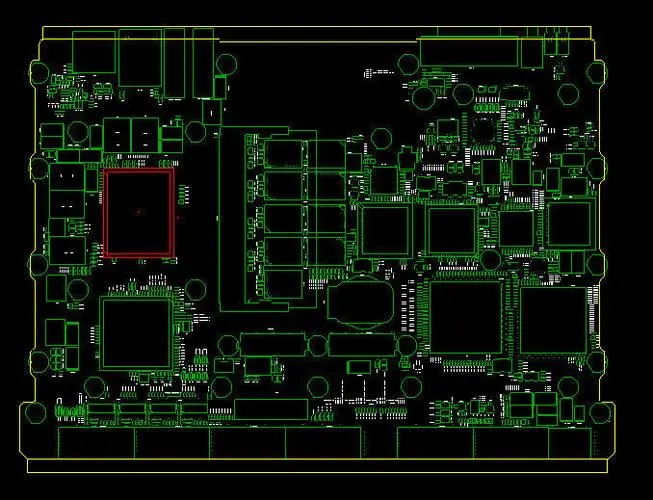

SDRAM尽量靠近MCU,缩短MCU到SDRAM的信号走线长度(一般不超过120mm);

2.保持SDRAM信号返回路径最短

对于多层PCB,高速信号的返回路径是其走线在参考平面上的投影。 在PCB设计中,应注意保持其参考平面的完整性和连续性。 如果由于信号换层或电源层划分造成信号返回路径被切断,则必须通过增加换层电容/换层地过孔和电源层跨接电容来保证SDRAM信号的最短返回路径。

3.将SDRAM信号(尤其是时钟信号)放在PCB的内层

在SDRAM信号中,时钟信号的辐射水平最强,可以通过将其置于PCB内层并用外层铜箔屏蔽来降低。

STM32的FMC接口设计为同时附有SDRAM和FLASH。 由于SDRAM和FLASH共用部分MCU管脚,其复杂的走线拓扑进一步增强了SDRAM信号的辐射干扰。 建议SDRAM和FLASH走线尽量走线在PCB内层,这些信号同时在PCB外层屏蔽。

4.使 SDRAM 布线区域尽可能远离其他信号/电缆

其他较长的走线或电缆可作为天线将耦合后的SDRAM辐射信号发出,因此应布置在PCB中远离SDRAM信号的区域。 必要时,可以在这些走线或电缆的连接端放置磁珠或滤波器,以衰减SDRAM的辐射信号。

然后

联系

电话热线

13410863085Q Q

微信

- 邮箱