ICT技术的边界扫描详解

在 80% 和 90% 的电路板制造商中,ICT 测试仪要求每个电路节点至少有一个测试点。 但是随着器件集成度的提高,功能越来越强,封装越来越小,SMT加工元器件越来越多,多层板的使用,PCBA板元器件密度越来越大,很难在每个节点都放置一个探针。 增加测试点,制造成本会增加; 同时,强大器件的测试库开发难度加大,开发周期延长。 为此,联合测试组织(JTAG)发布了IEEE1149.1测试标准。

IEEE 1149.1 定义了扫描设备的几个重要特性。 首先,定义构成测试访问端口(TAP)的四(五)个引脚:TDI、TDO、TCK、TMS、(TRST)。 测试模式选择(TMS)用于加载控制信息; 其次,定义了TAP控制器支持的几种不同的测试模式,主要包括外部测试、内部测试和运行测试; 最后,提出了边界扫描描述语言。 BSDL描述了扫描设备的重要信息。 它将管脚定义为输入、输出和双向类型,并定义了TAP的模式和指令集。

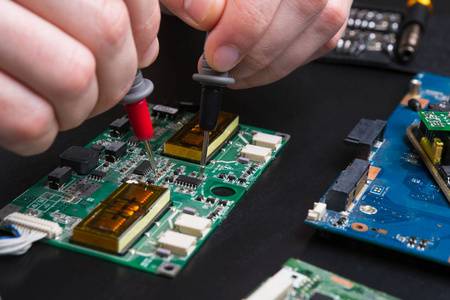

边界扫描器件的每个管脚都连接到串行移位寄存器(SSR)的一个单元,称为扫描单元。 扫描单元连接形成移位寄存器链来控制和检测器件引脚。 其特定的四个引脚用于完成测试任务。

多个扫描设备的扫描链通过它们的TAP连接起来,形成一个连续的边界寄存器链。 给链头添加TAP信号,控制和检测链上所有设备的管脚。 这种虚拟接触代替了针床治具在器件每个引脚上的物理接触,虚拟接入代替了实际的物理接入,去除了大量占用PCB板空间的测试焊盘,降低了PCB和治具的制造成本。

作为一种测试策略,在针对PCB板进行可测性设计时,可以使用专门的软件对具有扫描功能的电路点和器件进行分析,决定如何在不降低测试覆盖率的情况下有效地放置有限数量的测试点,从而减少测试 最经济的点和测试针。

边界扫描技术解决了不添加测试点的困难。 更重要的是,它提供了一种简单快速的测试图形生成方法。 使用软件工具,可以将BSDL文件转换成测试图形,例如Teradyne的Victory、GenRad的Basic Scan和Scan Path Finder。 解决编写复杂测试库的困难。

TAP 访问端口也可用于 CPLD、FPGA 和闪存的在线编程(In System Program 或 On board Program)。

然后

联系

电话热线

13410863085Q Q

微信

- 邮箱