根据相关EMC/EMI技术规范,将指标分解为单板电路进行分级控制。

控制EMI的三要素,即干扰源、能量耦合路径和敏感系统,使电路具有平坦的频率响应,保证电路的正常稳定工作。

从设备前端设计入手,关注EMC/EMI设计,降低设计成本。

数字电路PCB的EMI控制技术

在处理各种形式的EMI时,必须具体问题具体分析。 在数字电路的PCB设计中,EMI控制可以从以下几个方面进行。

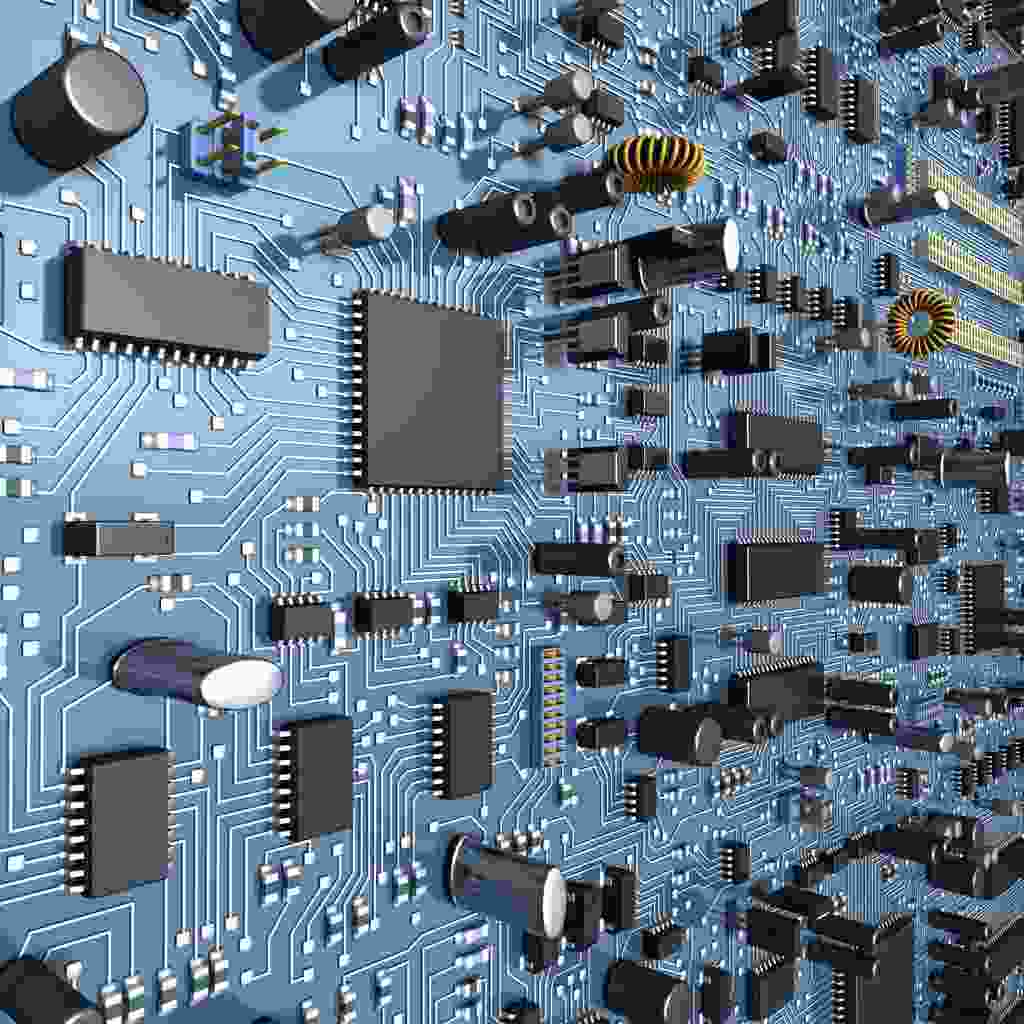

1.设备选择

在 EMI 设计中,应首先考虑所选器件的速度。 对于任何电路,如果将上升时间为5ns的器件换成上升时间为2.5ns的器件,EMI会增加4倍左右。 EMI的辐射强度与频率的平方成正比。 最高 EMI 频率 (fknee) 也称为 EMI 传输带宽,它是信号上升时间而非信号频率的函数:

Fknit=0.35/Tr(其中Tr为PCB器件信号上升时间)

这种辐射 EMI 的频率范围是 30MHz 到几 GHz。 在这个频段,波长很短,电路板上即使很短的布线也可能成为发射天线。 EMI高时,电路容易失去正常功能。 因此,在器件选择上,在保证电路性能要求的前提下,尽量采用低速芯片,并选用合适的驱动/接收电路。 另外,由于器件的引脚有寄生电感和电容,在高速设计中器件封装对信号的影响也不容忽视,因为它也是产生EMI辐射的重要因素。 一般SMD的寄生参数小于插件器件,BGA封装的寄生参数小于QFP封装。

2.连接器的选择和信号端子的定义

连接器是高速信号传输的关键环节,也是容易产生EMI的薄弱环节。 在连接器的端子设计中,可以布置更多的接地引脚,以减少信号与地之间的距离,减少连接器中产生辐射的有效信号环路面积,提供低阻抗返回路径。 如有必要,考虑用接地引脚隔离一些关键信号。

3.堆栈设计

在成本允许的前提下,增加地线层数,将信号层靠近地平面层放置,可以降低EMI辐射。 对于高速PCB,电源层和地层紧密耦合,可以降低电源阻抗,从而降低EMI。

4.PCB布局

根据信号电流的流向,合理布局可以减少信号间的干扰。 合理布局是控制EMI的关键。 布局的基本原则是:

模拟信号易受数字信号干扰,模拟电路应与数字电路分开;

时钟线是主要的干扰和辐射源,应远离敏感电路,时钟线最短;

大电流、高功耗电路尽量不要布置在板的中心区域,同时考虑散热和辐射的影响;

连接器尽量布置在板的一侧,远离高频电路;

输入/输出电路靠近相应的连接器,去耦电容靠近相应的电源引脚;

充分考虑分权布局的可行性。 多功率器件跨功率划分区边界放置,有效降低平面划分对EMI的影响;

返回平面(路径)没有被分割。

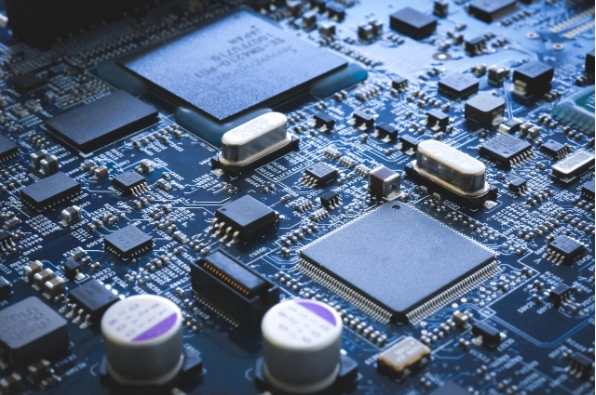

5.PCB布线

阻抗控制:高速信号线会表现出传输线的特性。 需要阻抗控制来避免信号的反射、过冲和振铃,并减少 EMI 辐射。

严格控制时钟信号(尤其是高速时钟信号)的走线长度、过孔数量、交叉分区、端接、布线层、返回路径等。

信号环路,即信号流出到信号流入所形成的环路,是PCB设计中EMI控制的关键,在布线时必须加以控制。 要了解每个关键信号的流向,关键信号应靠近返回路径布线,以确保最小环路面积。

数字电路PCB设计中的EMI控制技术

对于低频信号,电流应流经电阻最小的路径; 对于高频信号,高频电流应该流经电感最小的路径,而不是电阻最小的路径。 对于差模辐射,EMI 辐射强度 (E) 与电流、电流环路面积和频率的平方成正比。 (其中 I 是电流,A 是环路面积,f 是频率,r 是到环路中心的距离,k 是常数。)

因此,当最小电感返回路径刚好位于信号导体下方时,可以减小电流环路面积,从而降低EMI辐射能量。

其他EMI控制手段

1.电源系统设计

低阻抗供电系统旨在确保配电系统在低于fknee的频率范围内的阻抗低于目标阻抗。

使用滤波器控制传导干扰。

电源去耦。 在EMI设计中,合理的去耦电容可以使芯片可靠工作,降低电源中的高频噪声,降低EMI。 由于PCB导线电感和其他寄生参数的影响,电源及其供电导线的响应速度较慢,这将导致高速电路中驱动器所需的瞬时电流不足。 通过合理设计电源层的旁路或去耦电容和分布式电容,可以利用电容的储能功能,在电源响应之前快速为设备提供电流。 适当的电容去耦可以提供低阻抗的供电路径,这是降低共模EMI的关键。

2.接地

接地设计是降低整板EMI的关键。

应采用单点接地、多点接地或混合接地。

数字地、模拟地和噪声地应分开,并确定合适的公共接地点

双面板设计如果没有地线层,合理设计地线网格很重要,保证地线宽度>电源线宽度>信号线宽度。 也可以采用大面积铺地,但要注意同层大面积地的一致性好。

对于多层PCB板的设计,应保证地平面层,以降低共地阻抗。

3.串联阻尼电阻

在电路时序要求允许的前提下,抑制干扰源的基本技术是在关键信号输出端串联一个阻值较小的电阻,通常为22~33Ω。 这些串联在输出端的小电阻可以减缓上升/下降时间,使过冲和下冲信号更平滑,从而降低输出波形的高频谐波幅度,有效抑制EMI。

然后

联系

电话热线

13410863085Q Q

微信

- 邮箱