SMT working environment and methods to reduce voids

In the management and production of employees' working environment, the ISO9001-2008 system standard patch machine shall be strICtly implemented Introduce foreign advanced "5S" management concept The following is a brief sharing of the working environment management specifications

1. The SMT chip data management level shall formulate the data placement standard, and all data shall be placed in the rack and at the required location, with corresponding MARKs There are corresponding operation specifications for guiding data acquisition and replay, and corresponding records shall be made

2. Environmental management of SMT production workshop

The production management system shall be formulated in the production workshop of the placement machine, requiring the workshop personnel to observe the process discipline and operate in strict accordance with the operating procedures; All equipment, articles, raw materials and tools shall be free of dust; Stairs and floors are clean and free of rubbish; Doors and windows are clean and dust-free; The public passage is smooth and free of sundries; In order to achieve "one inspection per day" and "one inspection per day", there are corresponding inspections and records every day.

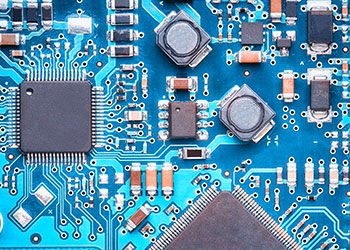

Circuit board

The cleanliness, temperature and humidity of the SMT chip locomotive room shall be controlLED according to the process files. Workshop air cleanliness is 100000 (BGJ73-84); In the air-conditioned environment, there must be a certain amount of fresh air, and try to control the CO2 content below 1000PPM and the CO content below 10PPM to ensure human health. The optimal ambient temperature of the workshop is 23 ± 3 ℃, and the limit temperature is 15-35 ℃; The relative humidity is 45% - 70% RH. Curtain the windows on the wall to avoid direct sunlight to the equipment. All operations are recorded in this manual. Lighting is arranged in the workshop, with the illumination of 800~1200lx. At least 300lx. When the illumination is low, local lighting should be set.

3. Control of supporting facilities of SMT machine

1. Power management and control of chip mounter

The power supply voltage shall be stable, generally single-phase AC 220V, three-phase AC 380V. After installation, the power supply of the machine needs to be grounded independently. Generally, 3-phase five wire connection pipes are used, and the working zero line of power supply is strictly separated from the protection line. Install line filter or AC voltage stabilizer in front of equipment transformer.

2. Air source control of mounting machine

Air supply pressure shall be included according to equipment requirements. Generally, the pressure is greater than 7KG/cm2. The compressed air is introduced into the corresponding equipment of the production line, equipped with a unified air source network, and the air compressor must be kept at a certain distance from the SMT production workshop; Compressed air shall be subject to oil removal, dust removal and dehydration.

3. Exhaust air volume control of SMT production line

Both reflow welding and wave soldering equipment have exhaust requirements, and exhaust fans are included according to equipment requirements. The minimum flow value of all hot blast furnace exhaust pipes is usually controlled at 500 cubic feet per minute.

SMT chip technology to reduce voids

Voids can occur when welding large flat and low foot height components, such as QFN components. The use of these types of components is being added. In order to meet IPC standards, the formation of voids has brought troubles to many designers, SMD production line operators and quality control personnel. This paper focuses on a new method to reduce voids.

The parameters to optimize the void efficiency are usually the chEMIcal composition of solder paste, the reflow temperature curve, the coating of substrates and components, and the design of pads and templates. However, in practice, changing these parameters has obvious limitations. Although a lot of optimization work has been carried out, it is still often seen that the level of porosity is too high.

Voids of different degrees

When we carefully observe the solder joints and cavities, one of the main parameters does not seem to attract people's attention. This is a solder alloy.

As a preliminary test, the three lead-free solder alloys commonly used in the market all have the characteristics of pore behavior.

Further research strategies include the use of tin, bismuth, silver, zinc, copper and other elements to adjust these alloys and observe their effects on the void behavior. Since this method can rapidly produce many alloys, this TGA analysis is used as an initial selection tool. Thermogravimetric analysis can be used to monitor the evaporation and reflow temperature distribution of the chemical composition of the flux in the bonding process with a certain alloy. Experience shows that a smoother evaporation curve usually means a lower level of pore formation. From this study, eight prototype solder alloys were selected and their void behavior was characterized.

To this end, 60 QFN coated with each alloy were welded on three different coated substrates: NiAu (ENIG), OSP and I-Sn. The chemical composition, template thickness and layout and substrate layout of the solder paste used in all alloys are the same. Use the welding temperature curve according to the melting point of the alloy. X-ray is used to determine the void content level. One of the alloys obtained the best results in terms of cavitation behavior and was selected for further mechanical reliability testing.

Introduction

For many years, the mechanism of void formation in solder joints has been the subject of research. Many void types and formation mechanisms have been identified. The most striking is the huge gap. It seems that the main factor for forming large voids is the chemical composition of the solder paste.

Micropores, shrinkage cavities and Kirkendall cavities are also well known and well documented

Type, but it is beyond the scope of this article. Over the years, many technologies have been established to reduce the formation of voids.

Adjusting the chemical composition of solder paste, reflow soldering temperature curve, component, PCB and template design or coating are some optimization tools widely used nowadays. Even equipment manufacturers are offering solutions to reduce porosity through frequency scanning or vacuum technology. However, there is another very important parameter that defines the pore formation of the welding alloy.

Welding alloy: an unusual and suSPIcious factor. The main cause of cavity formation has been considered to be the flux in the solder paste. It seems to be the right way to design a solder paste flux that can effectively reduce voids, because about 50% of the flux will evaporate during reflow, resulting in voids. As the focus of the research is solder paste flux, so far, the research on the difference of void formation of different solder alloys has not attracted enough attention.

Measure the porosity level with standard weldable alloy and determine the baseline porosity formation percentage, such as SnAg3Cu0.5 (SAC305), SnAg0.3Cu0.7 (LowSAC0307) and Sn42Bi57Ag1. All tests described in this document use the same paste chemistry.

In order to understand the level differences between PCB finishes, three commonly used finishes in the industry were tested:

OSPCu, ENIG (NiAu) and I-Sn In order to have enough clearance, a 120mm template is used without any reduction of PCB pads For each solder paste, use the standard heating reflow profile applicable to each specific solder alloy to reflow 60 tin coated QFN components

然后

联系

电话热线

13410863085Q Q

微信

- 邮箱