Wiring technology improves the integrity of embedded PCB

1 Introduction

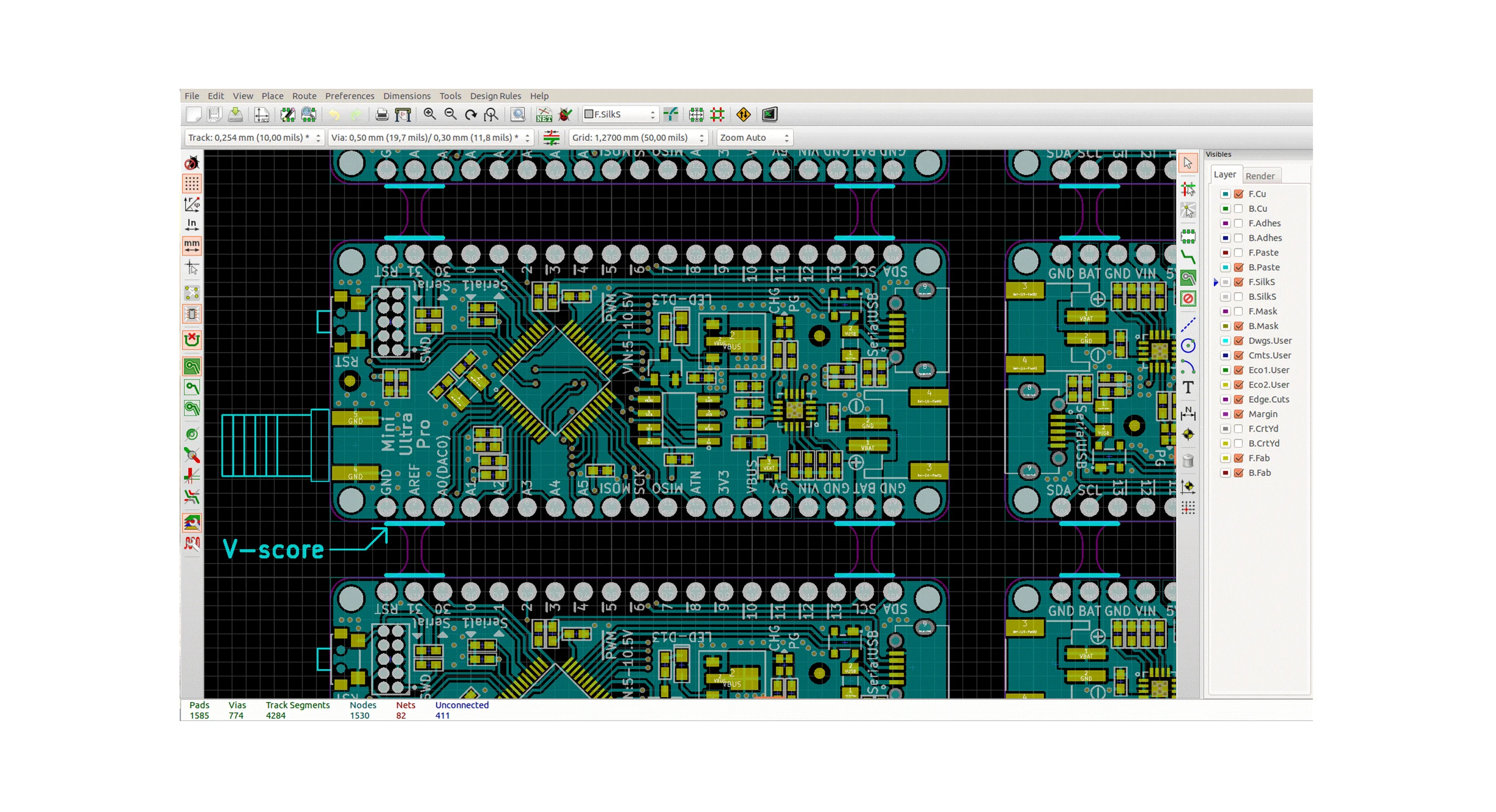

Printed circuit board is the basIC support of circuit components and devices in electronic products, and its design quality often directly affects the reliability and compatibility of embedded systems In the past, in some low-speed circuit boards, the clock frequency was usually only about 10 MHz The main challenge of circuit board or package design is how to route all signal lines on the double-layer board and how to assemble without destroying the package The electrical characteristics of the interconnects are not important because the interconnects do not affect system performance In this sense, the interconnects in the signal low speed circuit board are smooth and transparent However, with the development of embedded systems, the circuits used are basically high-frequency circuits Due to the new clock frequency, the rising edge of the signal has also been shortened. The capacitance and inductance reactance of the printed circuit to the signal will be much greater than the resistance of the printed circuit itself, which will seriously affect the integrity of the signal For embedded systems, when the clock frequency exceeds 100 MHz or the rising edge is less than 1 ns, the signal integrity effect becoMES very important Based on the actual power characteristics of signal lines in high-speed digital circuits, this paper establishes a power characteristic model, finds out the main reasons that affect signal integrity and how to solve the problems, and gives the problems that should be paid attention to in wiring and the methods and skills to follow

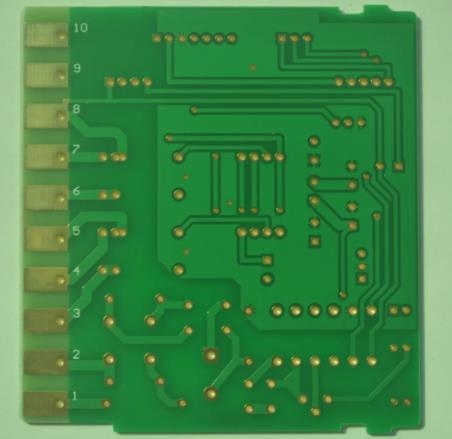

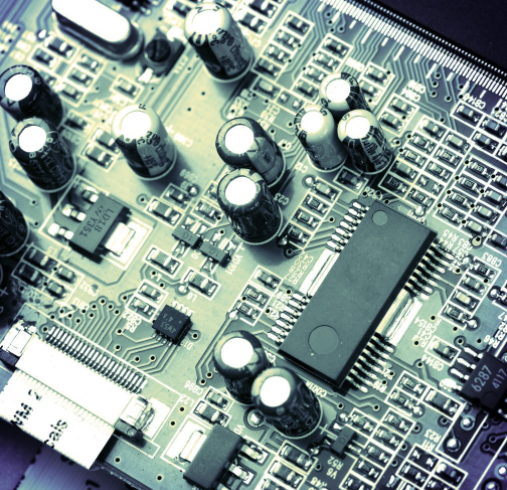

Printed circuit board

2. Signal integrity

Generally, it can be considered that the signal integrity should include the following meanings: the waveform distortion of the signal should be controlLED within a certain range, the sequence diagram of the signal flow can meet the logic requirements, and the signal generation and transmission process is stable under the burst state There are two main reasons for the destruction of signal integrity First, the original waveform is destroyed due to external interference, especially the interference of the conductive channel, including the reflection effect caused by the impedance miSMAtch of the transmission channel; Secondly, digital signal will naturally produce spectral dispersion effect and change the original waveform When the clock frequency is relatively high, for example, when the clock reaches 10MHz or higher, or the edge time of the pulse reaches 1ns or less, we will find that it is not easy to transmit the signal to the expected position There are many factors affecting signal integrity, including jitter, delay, ground bounce, reflection, crosstalk, switching noise, power mismatch, attenuation, pulse stretching, timing confusion, etc The problem of signal integrity always involves the whole process of signal. After all, signal integrity assurance requires the physical environment in which the whole signal works To achieve this, it is necessary to model the signal integrity system The signal integrity system model shall include three parts: complete signal source, physical coordination channel of signal, and complete signal reception The main contents of the three parts are as follows:

(1) Complete signal source: ensure the integrity of the generated signal. It includes power supply assurance, noise filtering, ground potential, common mode elimination, output impedance assurance, etc

(2) The physical coordination channel of the signal: Ensure that the signal does not change during transmission. These include crosstalk, delay, channel inclination, reflection and resonance, bandwidth, attenuation, impedance control, circuit connection, and more

(3) Complete signal reception: ensure high-efficiency reception without distortion. Including: input network signal distribution and signal protection issues

2.1 Delay: delay refers to the signal transmitted to PCB at a limited speed on the transmission line The signal is sent from the sender to the receiver, and there is a transmission delay between them Signal delay has influence on system timing; The propagation delay is mainly determined by the length of the wire and the dielectric constant of the medium around the wire In high-speed digital system, the length of signal transmission line is a direct factor affecting the phase difference of clock pulse The phase difference of clock pulse refers to the asynchronous time when two clock signals generated at the same time arrive at the receiver The phase difference of clock pulse reduces the predictability of signal edge arrival. If the phase difference of clock pulse is too large, it will generate an error signal at the receiver

2.2 Reflection: reflection is the echo of the signal on the signal line When the signal delay time is much greater than the signal transition time, the signal line must be used as a transmission line When the characteristic impedance of the transmission line does not match the load impedance, a port of the signal power (voltage or current) is transmitted to the line and reaches the load If the load impedance is less than the original impedance, the reflection is negative; Otherwise, the response will be positive This reflection is caused by changes in track geometry, incorrect wiring termination, transmission through connectors, and discontinuities in the power plane

2.3 Crosstalk: Crosstalk refers to the coupling between two signal lines, mutual inductance and capacitance between signal lines, and noise on signal lines Capacitive coupling causes coupling current and inductive coupling generates coupling voltage Crosstalk noise originates from electromagnetic coupling between signal lines, between signal system and power distribution system, and between through holes Cross winding may cause clock error, intermittent data error, etc, It also affects the transmission quality of adjacent signals In fact, crosstalk cannot be completely eliminated, but it can be controlled within the tolerable range of the system The parameters of the PCB layer, the distance between signal lines, the power characteristics of the driver and receiver, and the baseline termination method all have a certain impact on the crosstalk When high-speed wiring occurs to PCB boards, if the wiring space is small or the wiring density is high, the crosstalk problem is very serious, and the resulting electromagnetic interference will seriously affect the circuit signal In order to reduce crosstalk, the following measures can be taken during wiring: correctly terminate crosstalk sensitive signal lines, reduce coupling capacitance through impedance matching, and reduce crosstalk

2.4 Overshoot and undershoot: Overshoot is the peak or valley value exceeding the set voltage Voltage for rising edge; Voltage for falling edge Kick down refers to when the next valley value or peak value exceeds the set voltage Overshoot may cause the protection diode to work, leading to its premature failure Excessive undershoot can cause spurious clock or data errors (misoperations).

2.5 Oscillation and surround oscillation: the oscillation phenomenon is repeated overshoot and undershoot The signal oscillation is caused by the transitional inductance and capacitance on the line, which belongs to the under damping state, while the surrounding oscillation belongs to the over damping state Like reflection, oscillations and circular oscillations are caused by many factors. Proper termination can reduce the oscillations, but it cannot completely eliminate them Ground bounce noise and echo noise: When there is a large current surge in the circuit, it will cause ground bounce noise For example, when a large number of chip outputs are turned on at the same time, there will be a large transient current between the chip and the circuit board Inductance and resistance of chip package and power board will cause power supply noise, which will lead to voltage fluctuation and change on the real ground plane, and this noise will affect the behavior of other components The increase of load capacitance, the decrease of load resistance, the increase of grounding inductance, and the increase of switching devices will lead to the increase of ground bounce

3. Analysis of the electrical characteristics of the transmission channel

In a multi layer PCB, most transmission lines are not only arranged on a single layer, but interlaced on multiple layers, and each layer is connected by via Therefore, in a multilayer medium PCB, a typical transmission channel mainly includes three parts: transmission line, track corner, and through hole In the low frequency case, the printed circuit and tracking via can be regarded as the common electrical connection connecting different equipment pins, which has little impact on the signal quality However, at high frequencies, traces, corners and vias should not only consider their connectivity, but also the effects of their high-frequency electrical characteristics and parasitic parameters

4. High speed transmission line power characteristic analysis PCB board

In the design of High Speed PCB, it is inevitable to use a large number of signal connecting lines with different lengths Compared with the change time of the signal itself, the delay time of the signal passing through the connecting line cannot be ignored. The signal is transmitted at the speed of electromagnetic wave For upstream transmission, the connecting line is a complex network with resistance, capacitance, and inductance. It needs to be described by a distributed parameter system model, namely, the transmission line model The transmission line is used to transmit signals from one end to the other. It is composed of two wires with a certain length. One is called the signal path and the other is called the return path In low frequency circuits, the transmission line is purely resistive When driving at high speed, with the increase of the transmission signal frequency, the capacitive impedance between the conductors decreases, and the inductive impedance on the conductors increases. The signal line no longer behaves as a pure resistance. That is, the signal will not only be transmitted through the conductors, but also be transmitted in the medium between the conductors For the uniform conductor, the resistance R, the preliminary induction L and the preliminary capacity C of the transmission line are even distributed (ie, L1=L2=â ¦= Ln; C1=C2=â ¦= Cn+1) without considering the external environment change.

5. Power characteristic analysis of high-speed via PCB

Via, usually referring to the hole on the printed circuit board, is an important factor in multi-layer design of PCB boards The via can be used for fixed installation of plug-in components or inter layer interconnection From the process point of view, vias are generally divided into three categories: blind holes, embedded vias, and through vias The blind hole is located on the top and bottom surfaces of the printed circuit board, has a certain depth, and is used to connect the surface circuit and the bottom inner circuit The depth and diameter of the hole usually do not exceed a certain proportion Embedded via refers to the connection hole located in the inner layer of the printed circuit board, which will not extend to the surface of the circuit board The through-hole passes through the entire circuit board and can be used for inter layer interconnection or as a mounting hole for components Because the through-hole is easier to realize in the process and has lower cost, the printed circuit board generally uses the through-hole instead of the other two kinds of through-hole The through holes mentioned below are considered as through holes As a special transmission line, via not only generates parasitic capacitance to ground, but also parasitic inductance in high-speed circuit The effect of via parasitic capacitance on the circuit is mainly to slow down or deteriorate the rising edge of digital signal and reduce the circuit speed The smaller the parasitic capacitance of the via, the smaller the impact The main function of via parasitic inductance is to reduce the effectiveness of power supply bypass capacitor and make the filtering effect of the whole power supply worse

6. Contribution of transmission line corners to transmission channel signal integrity problems

When the printed line of the PCB board passes through the corner, the change of column line width is positive, and the characteristic impedance of the printed line will also change Because the width of the trajectory becomes wider when it passes the corner, the capacitance between the trajectory and the reference layer increases, and the characteristic impedance of the trajectory decreases Therefore, the characteristic impedance at the corner of the printing line is discontinuous, which will cause the signal to be reflected on the printing line and affect the signal integrity Comparison of reflection and transmission characteristics of different geometric angles: common PCB printing line corner geometry: right angle, round corner, internal and external 45 degree bevel, 45 degree external bevel The reflection and transmission characteristics of the corner points of different geometric shapes are different The order of excellent transmission characteristics is as follows: right angle<rounded corner<45 degree level cut inside and outside<45 degree outer bevel cut In the frequency range lower than 2GH, the geometric shape of the track angle has little influence on the signal transmission characteristics. With the increase of frequency, its influence increases significantly, especially the right angle It is recommended to bend the angle of the trajectory into a right angle and form a 45 degree inclined plane geometry, which itself has little impact on the signal integrity When the signal linewidth in high-density circuit boards is narrow, the delay accumulation caused by corner parasitic capacitance is usually unlikely to have a significant impact on signal integrity However, for high-frequency sensitive circuits, such as high-frequency clock lines, the cumulative effect of corner parasitic capacitors should be considered

然后

联系

电话热线

13410863085Q Q

微信

- 邮箱