PCB material selection and PCB wiring precautions for hybrid circuit

Q: In today's wireless communICation equipment, the RF part often adopts a miniaturized outdoor unit structure, while the RF part, the IF part of the outdoor unit, and the low-frequency circuit part that monitors the outdoor unit are often deployed on the same PCB. What are the material requirements for such PCB wiring? How to prevent interference among RF, IF and LF circuits?

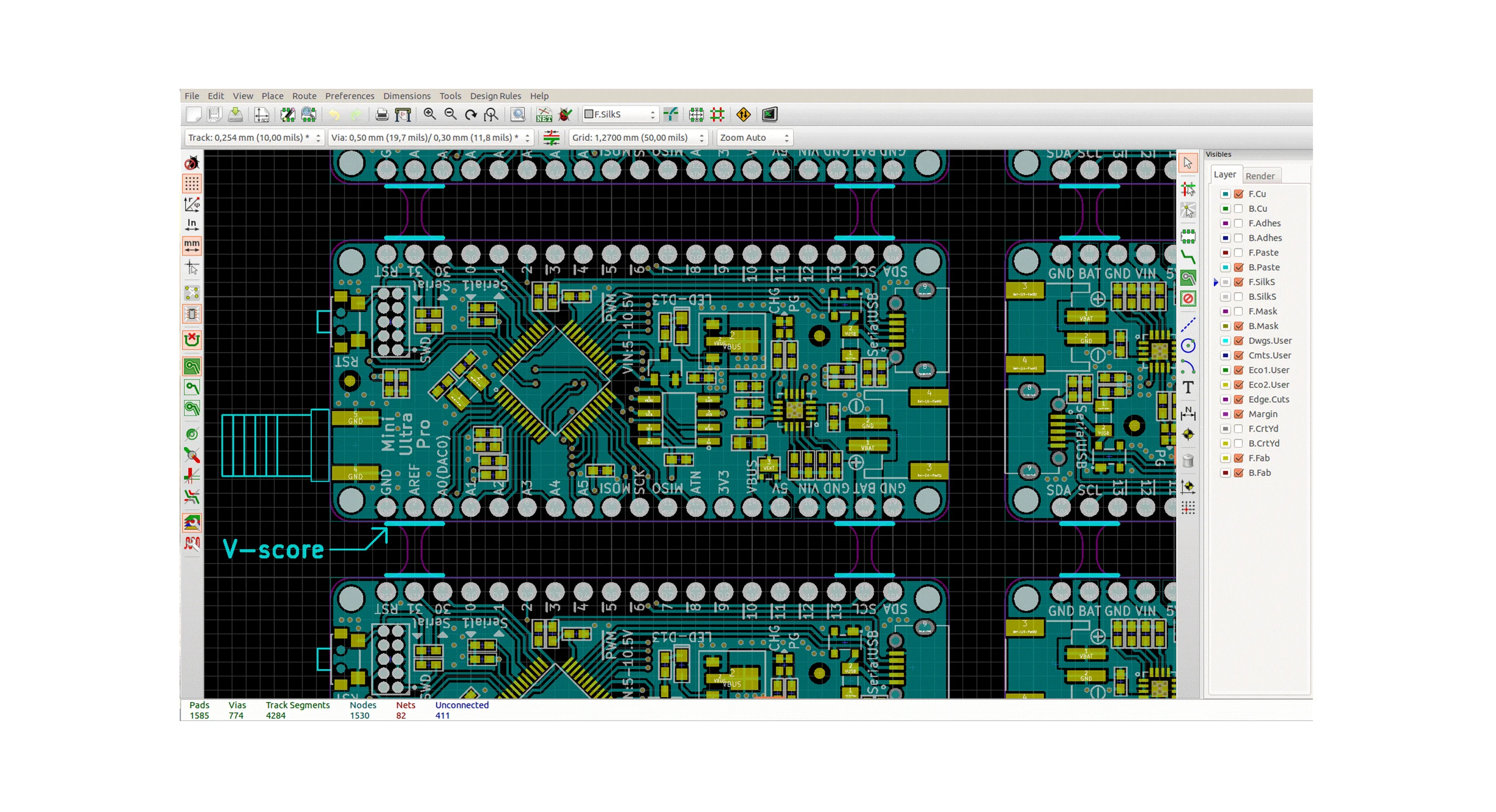

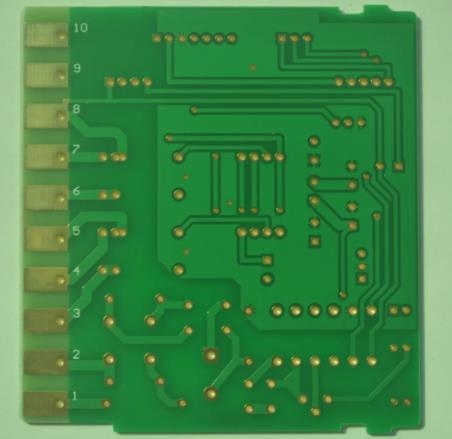

A: Hybrid circuit design is a big problem, and it is difficult to have a perfect solution. Generally, RF circuits are laid and routed as an independent board in the system, and even have a special shielding chamber. In addition, the RF circuit is generally a single or double sided board, and the circuit is relatively SIMple. All these are to reduce the impact on the distribution parameters of the RF circuit and improve the consistency of the RF system. Compared with the general FR4 material, RF circuit boards tend to use the substrate with high Q value. This material has SMAller dielectric constant, smaller distributed capacitance of transmission line, high impedance and small signal transmission delay.

In the hybrid circuit design, although RF and digital circuits are built on the same PCB, they are generally divided into RF circuit area and digital circuit area for layout and wiring. The grounding through hole tape and shielding box are used for shielding.

About the methods and rules of input and output termination

Q: In modern high-speed PCB design, in order to ensure signal integrity, it is often necessary to terminate the input or output terminals of devices. What are the termination methods? What factors determine the termination method? What are the rules?

A: Terminal, also calLED matching. Generally, there are active end matching and terminal matching according to matching position. The source end matching is generally resistance series matching, and the terminal matching is generally parallel matching. There are many ways, including resistance pull-up, resistance pull-down, Thevenin matching, AC matching, and Schottky diode matching. The matching mode is generally determined by BUFFER characteristics, topology, level type and decision mode, as well as signal duty cycle and system power consumption. The key of digital circuit is timing problem, and the purpose of adding matching is to improve the signal quality and get the determinable signal at the decision time. For the level effective signal, the signal quality is stable on the prEMIse of ensuring the establishment and retention time; For the delayed effective signal, the signal change delay speed meets the requirements on the premise of ensuring the single modulation of the signal.

What should I pay attention to when dealing with cabling density?

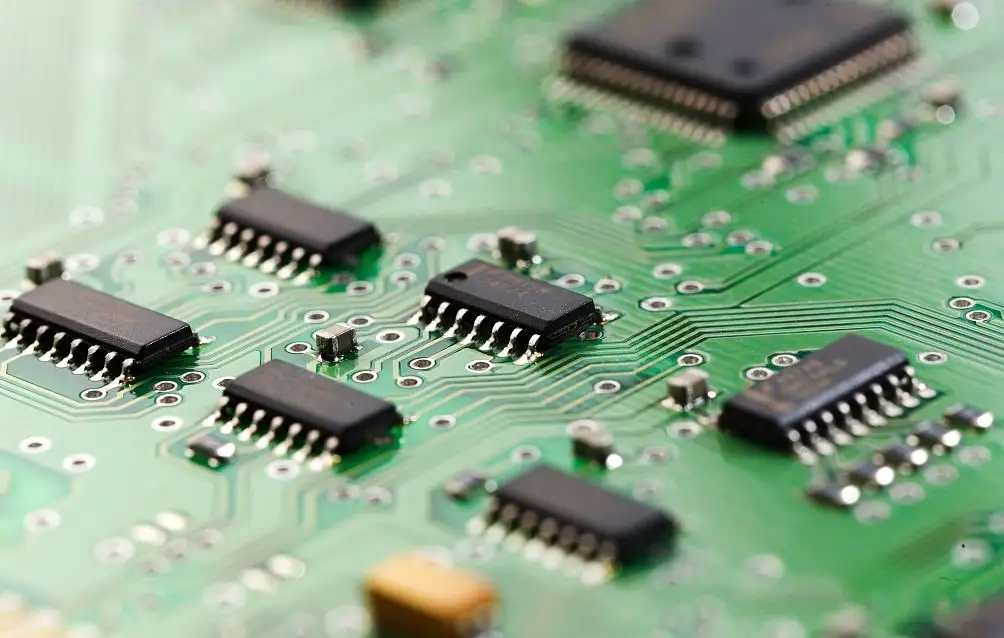

Q: When the size of the circuit board is fixed, if more functions need to be included in the design, it is often necessary to increase the wiring density of the PCB, but this may lead to increased mutual interference of the wiring, and at the same time, too thin wiring will not reduce the impedance. What are the skills in high-speed (100MHz) high-density PCB design?

A: When designing high-speed and high-density PCBs, we should pay special attention to crosstalk because it has a great impact on timing and signal integrity. The following points should be noted: 1. Control the continuity and matching of the characteristic impedance of the wiring. 2. Size of wiring spacing. Generally, the spacing is twice the line width. Through simulation, we can know the influence of routing distance on timing and signal integrity, and find out the minimum tolerable distance. Different chip signals may have different results. 3. Select an appropriate termination method. 4. Avoid the same routing direction of the upper and lower adjacent layers, or even the overlapping of the upper and lower layers, because this kind of crosstalk is greater than the adjacent routing of the same layer. 5. Use blind/buried via to increase wiring area. However, the production cost of PCB will increase. It is really difficult to achieve full parallelism and equal length in actual implementation, but we should try our best to do so. In addition, differential termination and common mode termination can be reserved to mitigate the impact on timing and signal integrity.

On Impedance Matching in PCB Design

Q: In order to prevent reflection, impedance matching must be considered in the design of high-Speed PCB. However, because PCB processing technology limits the continuity of impedance and simulation cannot imitate it, how to consider this problem in schematIC design? In addition, I do not know where to provide a more accurate IBIS model library. Most of the libraries we downloaded from the Internet are not accurate, which greatly affects the reference of the simulation.

Answer: When designing high-speed PCB circuits, impedance matching is one of the elements of design. The impedance value has an absolute relationship with the routing method. For example, when walking on the surface layer (microstrip) or the inner layer (stripe/double stripe), the distance from the reference layer (power layer or stratum), the routing width, PCB material, etc. will affect the characteristic impedance value of the routing. That is to say, the impedance value can be determined only after wiring. General simulation software can't take into account some discontinuous impedance wiring due to the limitation of line model or mathematical algorithm used. At this time, only some terminators (such as series resistance) can be reserved on the schematic diagram to mitigate the effect of discontinuous impedance wiring. The real fundamental solution to the problem is to avoid impedance discontinuity when wiring. The accuracy of IBIS model directly affects the simulation results. Basically IBIS can be regarded as the electrical characteristics data of the actual chip I/O buffer equivalent circuit, which can generally be converted from the SPICE model (measurement can also be used, but there are many restrictions). The SPICE data has an absolute relationship with the Chip Manufacturing, so the SPICE data of the same device provided by different chip manufacturers are different, and the data in the converted IBIS model will also vary accordingly. That is to say, if manufacturer A's devices are used, only they can provide accurate model data of their devices, because no one knows better than them what process their devices are made by. If the IBIS provided by the manufacturer is inaccurate, the fundamental solution is to constantly require the manufacturer to improve.

EMC and EMI Problems in High Speed PCB Design

Q: When designing high-speed PCB, the software we use only checks the set EMC and EMI rules. What aspects should designers consider the EMC and EMI rules? How to set rules?

Answer: Generally, radiation and conducted should be considered simultaneously in EMI/EMC design. The former belongs to the part with higher frequency (30MHz) and the latter belongs to the part with lower frequency (30MHz) 。 Therefore, we cannot only pay attention to the high frequency and ignore the low frequency. A good EMI/EMC design must take into account the position of components, the arrangement of PCB stacks, the way of important online, the selection of components, etc. at the beginning of the layout. If there is no better arrangement in advance, it will take twice the effort and increase the cost if it is resolved afterwards. For example, the position of the clock generator should not be close to the external connector as much as possible, the high-speed signal should go through the inner layer as much as possible and pay attention to the continuity of the characteristic impedance matching and the reference layer to reduce reflection, the slope rate of the signal pushed by the device should be as small as possible to reduce the high-frequency component, and when selecting the decoupling/bypass capacitor, pay attention to whether its frequency response meets the requirements to reduce the power layer noise. In addition, note that the return path of high-frequency signal current makes the loop area as small as possible (that is, the loop impedance is as small as possible) to reduce radiation. The range of high-frequency noise can also be controlled by dividing the stratum. Finally, properly select the chassis ground between PCB and housing.

Wiring Skills of High Speed Differential Signals

Q: When the PCB is close to the parallel high-speed differential signal line pair, under the condition of impedance matching, the mutual coupling of the two lines will bring many benefits. But some people think that this will increase the signal attenuation and affect the transmission distance. Why? On the evaluation boards of some large companies, I found that some high-speed cabling is as close and parallel as possible, while others intentionally make the distance between two lines vary from one another. Which is better? My signal is above 1GHz and the impedance is 50 ohms. When using software to calculate, is the differential line pair also calculated in 50 ohms? Or 100 ohms? Can a matching resistance be added between differential line pairs at the receiving end?

A: One reason for the attenuation of high-frequency signal energy is the conductor loss, including skin effect, and the other is the dielectric loss of dielectric materials. When analyzing the transmission line effect in electromagnetic theory, we can see the influence of these two factors on signal attenuation. The coupling of differential lines will affect their respective characteristic impedance and become smaller. According to the voltage divider principle, this will make the voltage of the signal source to the line smaller. As for the theoretical analysis of signal attenuation due to coupling, I have not seen it, so I cannot comment on it. The wiring of differential pairs should be properly close and parallel. The so-called appropriate approach is because this distance will affect the value of differential impedance, which is an important parameter for designing differential pairs. The need for parallelism is also due to the need to maintain the consistency of differential impedance. If the two lines are either far or near, the differential impedance will be inconsistent, which will affect signal integrity and timing delay. The differential impedance is calculated as 2 (Z11 - Z12), where Z11 is the characteristic impedance of the PCB wiring itself, and Z12 is the impedance generated by the coupling between two differential lines, related to the line spacing. Therefore, when the differential impedance is designed to be 100 ohms, the characteristic impedance of the wiring itself must be slightly greater than 50 ohms. As for the size, it can be calculated by simulation software. The matching resistance between differential line pairs at the receiving end is usually added, and its value should be equal to the value of differential PCB impedance. This will improve the signal quality.

然后

联系

电话热线

13410863085Q Q

微信

- 邮箱