PCB厂工程师详细讲解DDR PCB布局规则

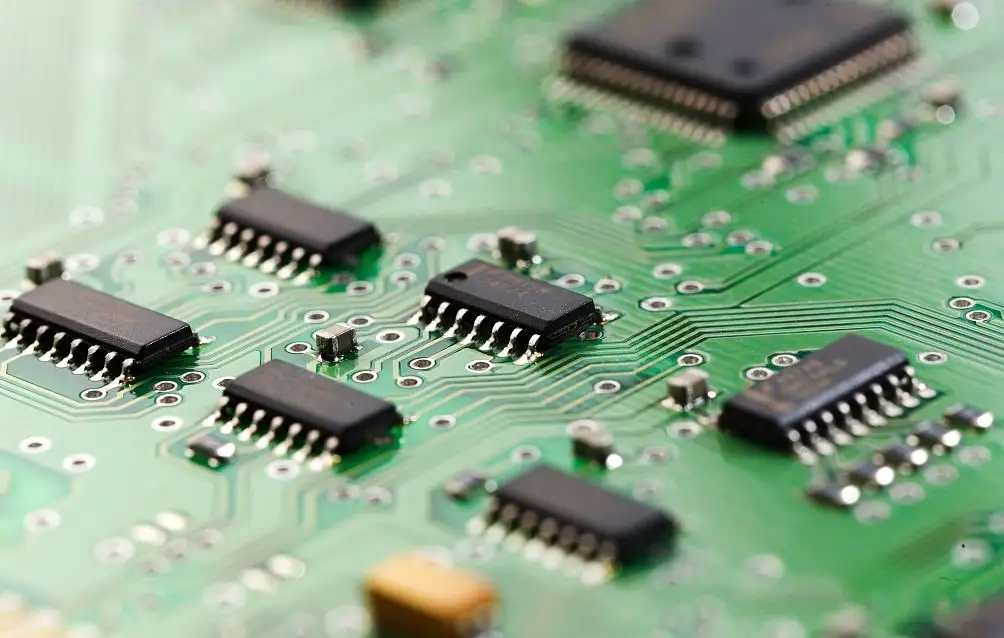

在普通印制电路板的布线中,由于信号是低速信号,所以一般在3W原则的基本布线规则下按照信号的流向进行连接就可以了。 但如果信号速度在100M以上,布线就很有讲究了。 最近已经发布了速度高达300M的DDR信号,仔细解释一下DDR信号的布线原理和技巧。

高速系统一般采用电压低、摆幅小的低压信号,容易提高速度、降低功耗,但这给布线带来困难。 因为低压信号功率受信号线内阻的影响较大,也就是电压与平方的关系,所以应尽量减小内阻,如采用电平面、多打孔等 ,缩短布线距离,并在高压传输末端使用电阻将较低电压信号分开。 SDRAM、DDR-I、DDR-II和DDR-III信号电压相互较低,这使得它越来越难以稳定。 供电还应注意,如果供电不足,内存将无法稳定工作。 信号完整性和传输线的概念是一门专业性很强的系统知识,这里不再详细介绍。 即使您不理解信号完整性和传输线的概念,也请遵循以下一般基本规则。 DDR高速信号板不会有问题。

1)DDR与主控芯片尽量靠近。 DDR高速信号中所有差分信号对的长度必须严格相等(最多允许50mils冗余)。 所有信号线和时钟线的长度不得超过2500mil,并尽可能允许过零过孔。 元件层下方必须有良好接地的地层,所有走线不得跨越地分割槽,即从元件层角度看不到与信号线交叉的地层分割线。 这样400M DDR就基本可以了。 其他3W、20H规则可以尽量执行。

2)地址和命令信号组:保持完整的地层和电源层。 特性阻抗控制在50~60Ω。 信号组与其他非DDR信号之间的距离至少为20mil。 组内信号应与 DDR 时钟线的长度匹配,间隙至少为 500 mil。 串联匹配电阻的RS值为O~33Ω,并联匹配电阻的RT值为25~68Ω。 该组中的信号不应与数据信号组位于同一电阻组中。

3)控制信号组:控制信号组信号最少,只有时钟使能和片选信号。 仍然需要完整的接地层和电源层以供参考。 串联匹配电阻RS值为O~33Ω,并联匹配终端电阻RT值为25~68Ω。 为了防止串扰,该组信号不能与数据信号位于同一电阻组中。

4)数据信号组:以地平面为参考,为信号电路提供完整的地平面。 特性阻抗控制在50~60Ω。 线宽与时钟信号宽度一致。 与其他非 DDR 信号至少相距 20 mil。 长度匹配由字节通道设置。 每个字节通道中的数据信号DQ、数据选通DQS和数据屏蔽信号DM的长度差应控制在±100mil以内(非常重要),不同字节通道内的信号长度差应控制在500mil以内。 匹配的DM、DQS的串联匹配电阻RS值为0~33Ω,并联匹配终端电阻RT值为25~68Ω。 如果电阻组用于匹配,则数据电阻组中不应有其他 DDR 信号。

5)时钟信号:以地平面为参考,为整个时钟环路的走线提供完整的地平面,为环路电流提供低阻抗路径。 由于是差分时钟信号,布线前需提前设计好线宽和线距,并根据此约束在布线前了解CPU的差分阻抗要求。 所有DDR差分时钟信号必须在关键平面上布线,以避免层间转换。 线宽和差分间距要保证3W的原则。 信号线单线阻抗控制在50~60Ω,差分阻抗控制在100~120Ω。 时钟信号与其他信号的距离应保持在20mil*以上,以防止与其他信号的干扰。 蛇形布线的间距不应小于20mil。 串联终端电阻RS值为15~33Ω,可选并联终端电阻RT值为25~68Ω。 (原理图设计时需连接终端电阻)

6)电源部分,去耦电容应放置在芯片电源引脚附近。 电源和地应有独立层,以便就近低阻信号返回。 电源和地层应尽可能多地钻孔,以保证电气连接良好、顺畅。

只要遵循以上的规则和技巧,从LAYOUT出来的DDR高速信号就不会有问题。 在对各信号进行等长处理时,为了保证信号线长度的允许误差,可以有意采用迂回路径处理。 一般采用蛇形线走线。 我们经常看到“等长布线”。 其实等长并不是目的,真正的目的是满足建立和保持时间、频率和相位相同、采样正确。 等长只是实现这一目标最简单的方法,这就需要对线长进行定量分析。 在在线特性阻抗控制方面,一般应要求线路的粗细,但每个板卡制造商的制造工艺和介电常数都不同,因此应要求板卡制造商控制信号线的特性阻抗。

然后

联系

电话热线

13410863085Q Q

微信

- 邮箱