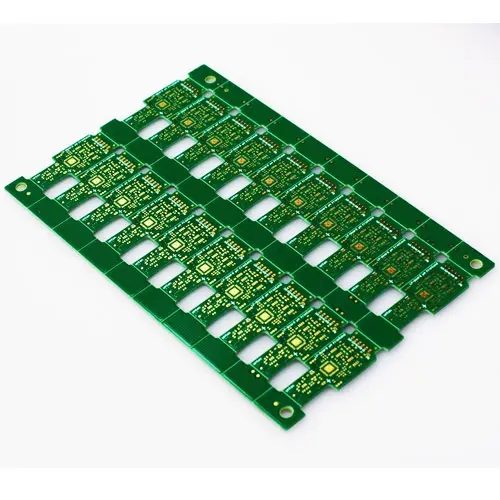

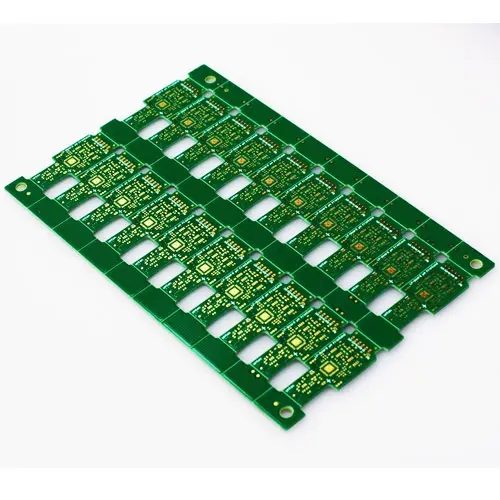

SDRAM原理设计及PCB设计布局规则

与传统的SDRAM接口电路相比,注册式SDARM电路对电路电参数的设计约束相对宽松,设计时基本不考虑主控芯片的驱动能力; 但由于Registered SDRAM也是一种高速接口电路,其电路设计也应遵循一定的规则,以保证所设计电路的可靠性和稳定性。

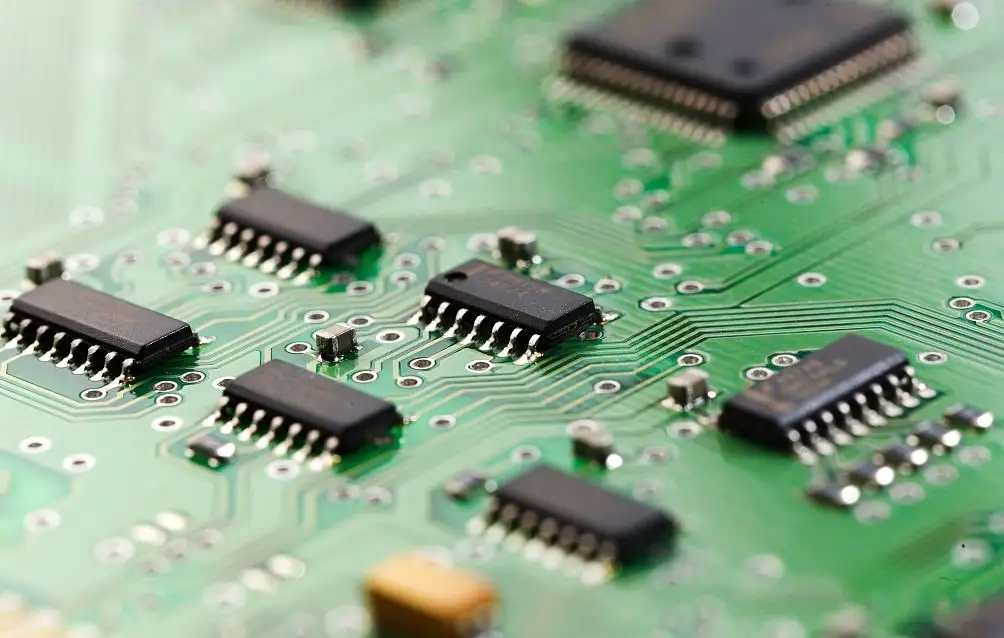

(一)原理设计规则

① 各芯片时钟输入端设计相位调整电容。 电容值可设置为10pF,可根据测量数据进行调整。

② 在每个SDRAM芯片的数据引脚中,串联设计了匹配电阻。 匹配电阻值可设置为l0Ω。

③ 每个锁存器芯片的锁存时钟使用时钟扩展电路的不同输出时钟。

④ 每个SDRAM芯片的输入时钟采用不同的时钟扩展电路的输出时钟。

⑤ 在时钟扩展芯片的时钟输出引脚处设计串联匹配电阻。 匹配电阻值可设置为l0Ω。

⑥ 锁存器芯片的输出端设计有串接匹配电阻。 匹配电阻值可设置为lOΩ。

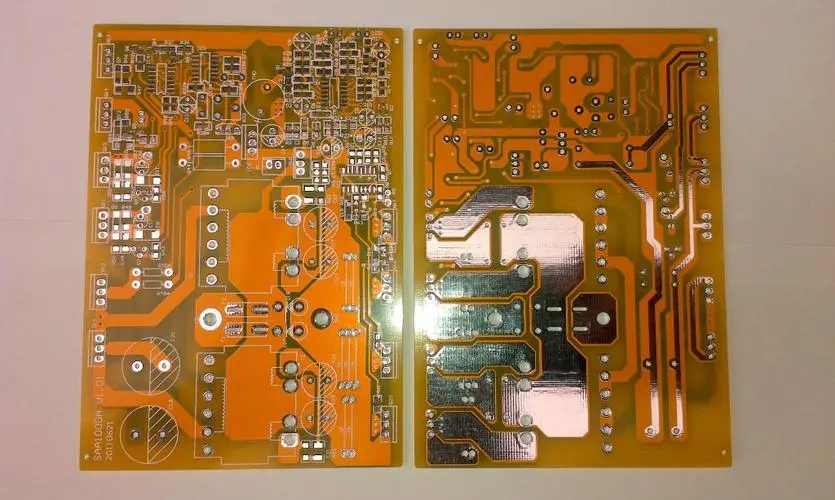

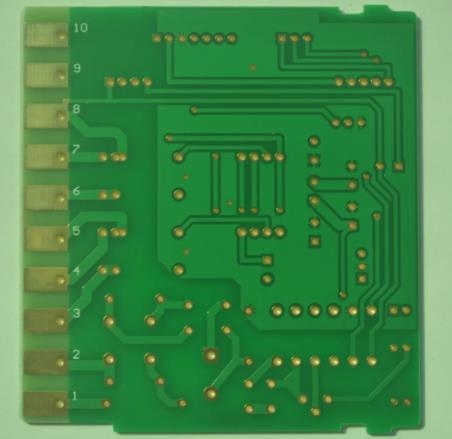

(二) 主板走线规则

① SDRAM数据线:从MPC824l到同一SDRAM芯片的数据信号走线需要控制等长,长度误差控制在±5%以内。

② SDRAM地址/控制线:锁存芯片到SDRAM芯片的地址/控制信号走线需控制等长,长度误差应控制在±5%以内。

③时钟扩展电路输出2路锁存时钟给锁存芯片。 其走线需控制等长,长度误差控制在±27mm以内。

④时钟扩展电路输出4路时钟到SDRAM芯片,其走线需要控制等长,长度误差控制在±1 27 mm以内。

⑤锁存器芯片到SDRAM芯片的地址/控制信号与时钟扩展电路到对应SDRAM芯片的时钟线长度基本相同,长度误差控制在±5%以内。

⑥时钟扩展电路的反馈时钟走线长度基本等于时钟扩展电路到SDRAM芯片的平均时钟走线长度,长度误差控制在±10%以内。

⑦MPC824l与SDRAM芯片之间的数据线、地址线、控制线、时钟线的走线长度基本相等,长度误差控制在±10%以内。

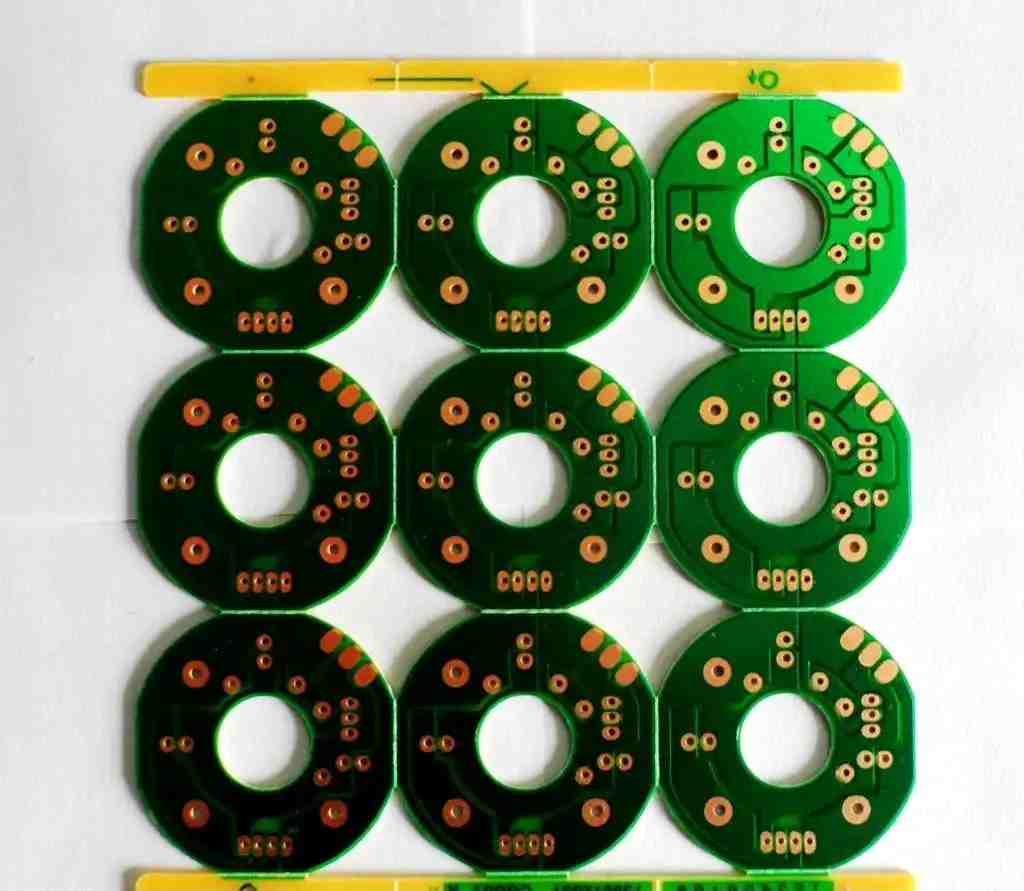

(三)布局规则

① 所有调相电容均置于接收端附近。

② 所有时钟串联匹配电阻均靠近发送端放置。

③SDRAM芯片数据引脚的串行匹配电阻靠近SDRAM芯片。

④锁存芯片输出端串联匹配电阻靠近输出端放置。

(四)其他设计规则

① 每根接线均进行阻抗控制,即单端线采用50Ω阻抗。

②芯片的电源引脚必须配备去耦电容,电容值为O一μF。原则上每个电源引脚都必须设计去耦电容,并尽可能靠近电源引脚布置。

③ 完整的地层和供电层至少应保证地层完整。

④时钟信号尽量走内层,以减少EMI。

(五)设计电路的调试

按照上述规则设计的硬件PCB电路只需稍微调整相位调整电容即可稳定工作在100 MHz SDRAM时钟下。 调相电容的范围一般为5~15pF。 如果定时参数余量足够,调相电容也可以不焊接。

然后

联系

电话热线

13410863085Q Q

微信

- 邮箱