高速PCB布局常见问题及解决方法

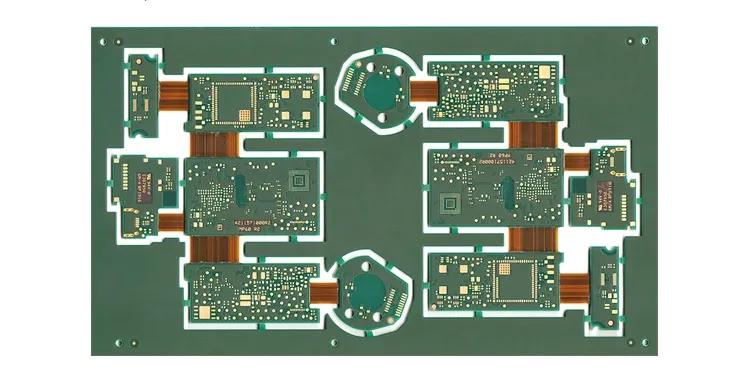

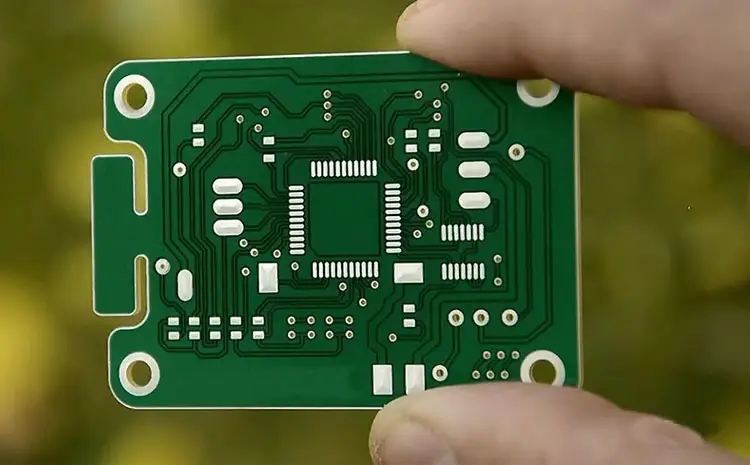

随着器件的工作频率越来越高,高速PCB设计面临的信号完整性等问题已成为传统设计的瓶颈,工程师在设计完整的解决方案时面临着越来越多的挑战。 虽然相关的高速仿真工具和互连工具可以帮助设计人员解决一些问题,但高速PCB设计还需要经验的不断积累和业界之间的深入交流。

以下是一些受到广泛关注的问题:

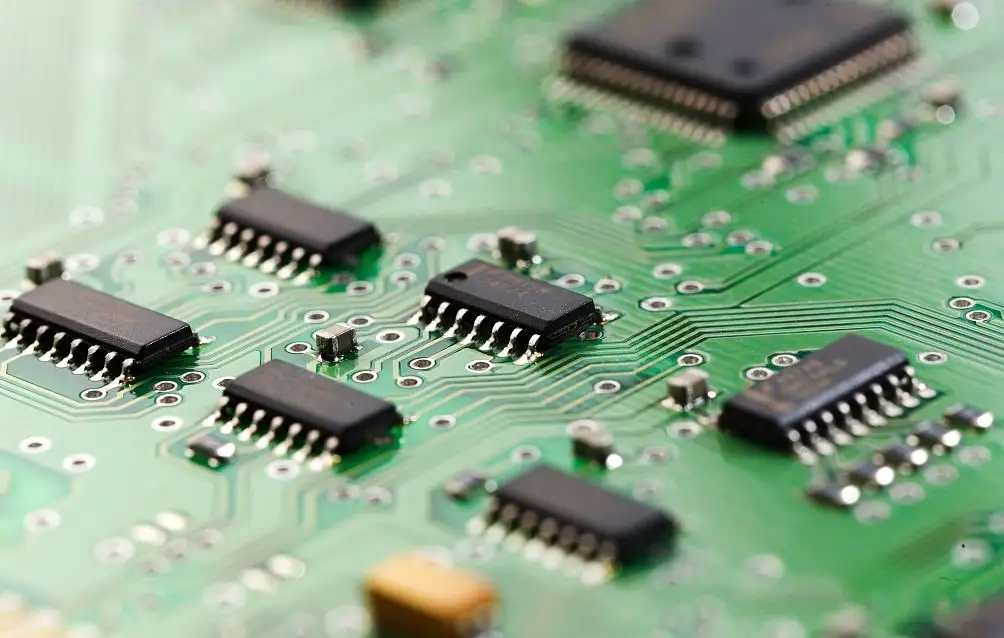

pad对高速信号的影响

在PCB中,从设计的角度来看,过孔主要由两部分组成:中间的钻孔和钻孔周围的焊盘。 焊盘对高速信号有影响,从而影响类似器件的封装。 详细分析可知,信号从IC出来后,经过焊线、引脚、封装外壳、焊盘和焊料到达传输线。 这个过程中的所有接头都会影响信号的质量。 但在实际分析中,很难给出焊盘、焊料、引脚的具体参数。 因此,一般用IBIS模型中的封装参数来概括。 当然,这种分析可以在较低频率下接收,但对于较高频率信号的更高精度模拟还不够准确。 现在的一个趋势是用IBIS V-I和V-T曲线来描述Buffer特性,用SPICE模型来描述封装参数。

布线拓扑对信号完整性的影响

当信号沿着高速PCB板上的传输线传输时,可能会导致信号完整性问题。 STC网友童阳问:对于一组总线(地址、数据、命令)最多驱动4、5个设备(FLASH、SDRAM等),PCB布线时,总线是否依次到达每个设备 比如先连接SDRAM,再连接FLASH……或者总线是否是星型分布的,即分开一处,分别连接各个设备。 这两种方法哪一种在信号完整性方面更好?

路由拓扑对信号完整性的影响主要体现在信号到达各节点的时间不一致,以及反射信号到达某个节点的时间不一致,从而导致信号质量恶化。 一般来说,星型拓扑可以通过控制多个相同长度的分支,使信号传输和反射延迟一致,以达到更好的信号质量。 使用拓扑时要考虑信号拓扑节点、实际工作原理和接线难度。 不同的Buffer对信号的反射效果不同,因此星型拓扑无法解决上述数据地址总线到FLASH和SDRAM的连接延迟问题,从而无法保证信号质量; 另一方面,DSP和SDRAM之间通常采用高速信号通信,FLASH加载速度不高。 因此,高速仿真时,不必关注FLASH处的波形,只要保证实际高速信号有效工作的节点处的波形即可; 与菊花链拓扑相比,星型拓扑的布线难度更大,尤其是当大量数据地址信号采用星型拓扑时。

RF 走线是过孔还是弯曲

在高速PCB中,它也可以减少很多返回路径,但有人表示宁愿将其弯曲也不愿将其打开。 他们应该如何选择?

分析射频电路的返回路径,与高速数字电路中的信号返回路径不同。 两者有一个共同点,都是分布参数电路,都应用麦克斯韦方程来计算电路的特性。 然而,RF电路是模拟电路,需要控制电压V=V(t)和电流I=I(t)两个变量,而数字电路只关注信号电压V=V(t)的变化( t)。 因此,在射频布线中,除了信号返回外,还应考虑布线对电流的影响。 即布线和过孔的弯曲是否会影响信号电流。 另外,大多数射频板都是单面或双面PCB,没有完整的平面层。 返回路径分布在信号周围和电源上。 在仿真过程中,需要使用3D场提取工具进行分析。 这时需要具体分析弯曲布线和过孔的回流; 高速数字电路分析一般只处理具有完整平面层的多层PCB。 使用二维场提取分析。 仅考虑相邻平面中的信号回流,并且过孔仅作为集总参数的 R-L-C 进行处理。

如何抑制电磁干扰

PCB是电磁干扰(EMI)的来源,因此PCB设计直接关系到电子产品的电磁兼容性(EMC)。 如果在高速PCB设计中关注EMC/EMI,将有助于缩短产品开发周期,加快上市时间。 因此,本次论坛上很多工程师都非常关注电磁干扰抑制问题。 例如,无锡祥生医学影像有限公司的舒健表示,在EMC测试中,时钟信号的谐波超标非常严重。 您想对使用时钟信号的IC的电源引脚进行特殊处理吗? 目前,只有去耦电容连接到电源引脚。 PCB设计中抑制电磁辐射还需要注意哪些方面? 对此,李宝龙指出,电磁兼容的三要素是辐射源、传播途径和受害者。 传输途径分为空间辐射传输和电缆传输。 所以要抑制谐波,首先要看它的传播路径。 电源的去耦是为了解决导通方式的传输。 此外,还需要必要的匹配和屏蔽。

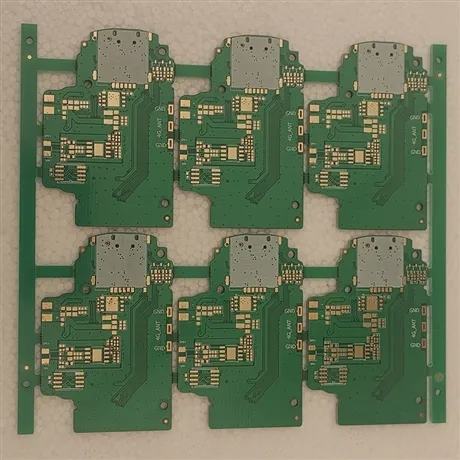

滤波是通过传导路径解决 EMC 辐射的好方法。 此外,还可以从干扰源和受害人方面考虑。 在干扰源方面,尝试用示波器检查信号上升沿是否太快,是否有反射或过冲、下冲或振铃。 如果有,考虑匹配; 另外,应尽量避免50%占空比的信号,因为该信号没有偶次谐波,高频成分较多。 对于受害者,可以考虑征地等措施。 电路板组装、电路板设计、电路板加工厂家讲解高速电路板布局中的常见问题及解决方案。

然后

联系

电话热线

13410863085Q Q

微信

- 邮箱