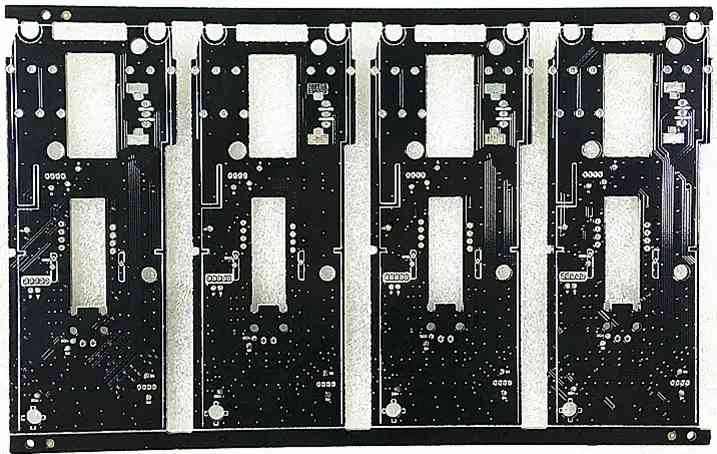

PCB设计评估中应注意的方面说明

在评估过程中,设计师必须问自己:什么标准对他们来说至关重要?

让我们看一下迫使设计人员重新检查其现有开发工具功能并开始订购新工具的一些趋势:

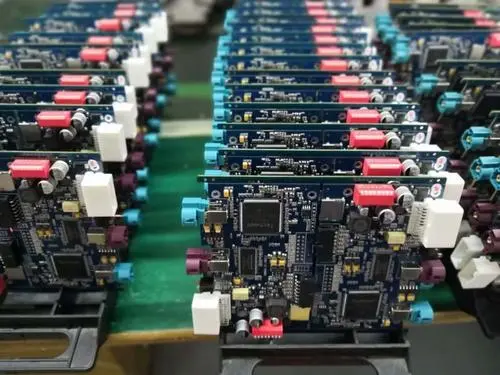

1、人类发展指数

半导体复杂性和逻辑门总数的增加要求集成电路有更多的引脚和更细的引脚间距。 在引脚间距为1mm的BGA器件上设计超过2000个引脚是很常见的,更不用说在引脚间距为0.65mm的器件上布置296个引脚了。 对更快的上升时间和信号完整性 (SI) 的需求需要更多的电源和接地引脚,这需要多层板中的更多层,从而推动对微通孔高密度互连 (HDI) 技术的需求。

HDI就是针对上述需求而开发的互连技术。 微过孔和超薄电介质、更薄的布线和更小的线距是HDI技术的主要特点。

2、射频设计

对于射频设计,射频电路应该直接设计成系统原理图和系统板布局,而不是单独的环境进行后续转换。 RF仿真环境的所有仿真、调谐和优化能力仍然是必要的,但仿真环境可以接受比“实际”设计更多的原始数据。 因此,数据模型之间的差异以及由此引起的设计转换问题将消失。 首先,设计人员可以直接在系统设计和射频仿真之间进行交互; 其次,如果设计人员进行大规模或相当复杂的射频设计,他们可能希望将电路仿真任务分配给多个并行运行的计算平台,或者他们可能希望将由多个模块组成的设计中的每个电路发送到各自的计算平台。 模拟器,以缩短模拟时间。

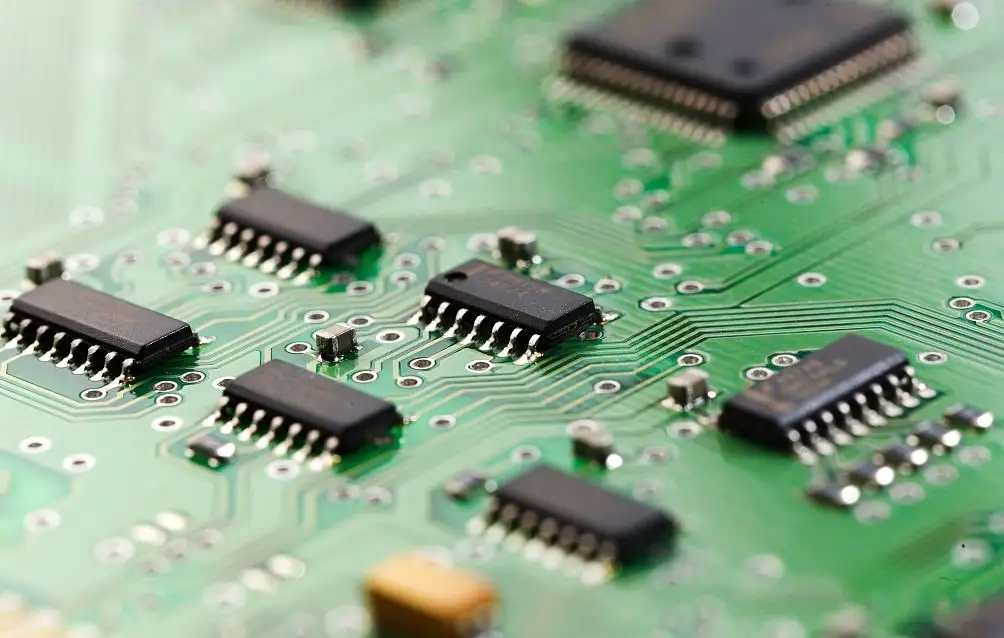

3、先进封装

现代产品功能日益复杂,要求无源元件数量相应增加,主要体现在低功率和高频应用中去耦电容和终端匹配电阻数量的增加。 尽管无源表面贴装器件的封装在几年后已经大幅缩小,但当试图获得最大极限密度时,结果仍然相同。 印刷元件技术已从多芯片模块(MCM)和混合模块转变为当今可直接用作嵌入式无源元件的SiP和PCB。 在改造过程中,采用了最新的装配技术。 例如,分层结构中包含阻抗材料层,在uBGA封装下直接使用串联终端电阻,大大提高了电路的性能。 现在,嵌入式无源元件可以获得高精度设计,从而消除激光清洁焊缝的额外加工步骤。 无线元件也正在朝着提高直接在基板中集成度的方向发展。

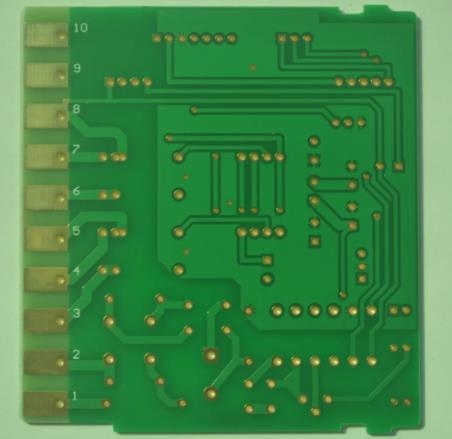

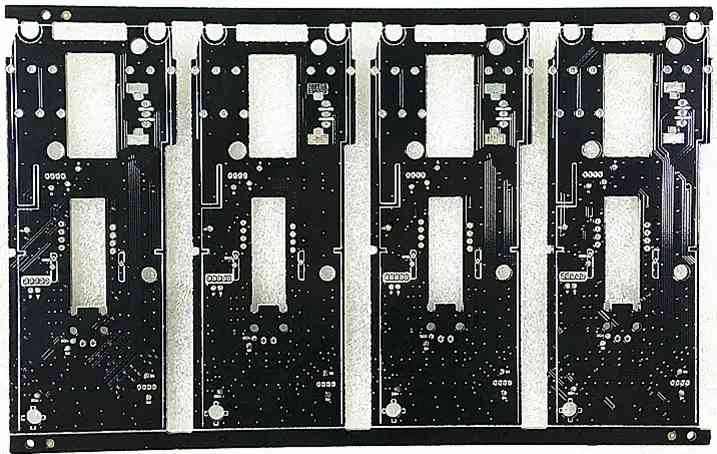

4、 刚挠性PCB

为了设计刚柔结合PCB,必须考虑影响组装工艺的所有因素。 设计者不能简单地将刚挠性PCB设计为刚性PCB,就像刚挠性PCB只是另一种刚性PCB一样。 他们必须管理设计的弯曲区域,以确保设计点不会因弯曲表面的应力作用而导致导体断裂和剥落。 仍有许多机械因素需要考虑,例如最小弯曲半径、电介质厚度和类型、金属板重量、铜镀层、整体电路厚度、层数和弯曲数量。了解刚柔结合设计并决定您的产品是否允许您创建刚柔结合设计。

5、信号完整性规划

近年来,与用于串并转换或串行互连的并行总线结构和差分对结构相关的新技术不断取得进展。

并行总线和串并转换设计中遇到的典型设计问题类型。 并行总线设计的局限性在于系统时序的变化,例如时钟偏差和传播延迟。 由于总线宽度上的时钟偏差,设计时序约束仍然很困难。 提高时钟速度只会使问题变得更糟。

另一方面,差分对架构在硬件层面采用可交换的点对点连接来实现串行通信。 通常,它通过单向串行“通道”传输数据,该通道可以堆叠为 1、2、4、8、16 和 32 宽度配置。 每个通道承载一个字节的数据,因此总线可以处理从 8 字节到 256 字节的数据宽度,并且可以通过使用某种形式的错误检测技术来维护数据完整性。 然而,高数据速率会导致其他设计问题。 高频下的时钟恢复成为系统的沉重负担,因为时钟需要快速锁定输入数据流,并且为了提高电路的抗抖动性能,还需要减少所有周期之间的抖动。 电源噪声还给设计人员带来了额外的问题。 这种类型的噪声增加了严重抖动的可能性,这将使眼图睁开更加困难。 另一个挑战是降低共模噪声并解决 IC 封装、PCB 板、电缆和连接器损耗影响所引起的问题。

6、设计套件的实用性

USB、DDR/DDR2、PCI-X、PCI Express、RocketIO等设计套件无疑将帮助设计人员进入新技术领域。 该设计套件概述并详细描述了该技术以及设计人员将面临的困难,然后进行了仿真以及如何创建布线约束。 它与程序一起提供了解释性文档,为设计人员提供了掌握先进新技术的第一次机会。

似乎很容易获得一个可以处理PCB布局的PCB工具; 但获得一款既能满足布局又能解决燃眉之急的工具至关重要。

然后

联系

电话热线

13410863085Q Q

微信

- 邮箱