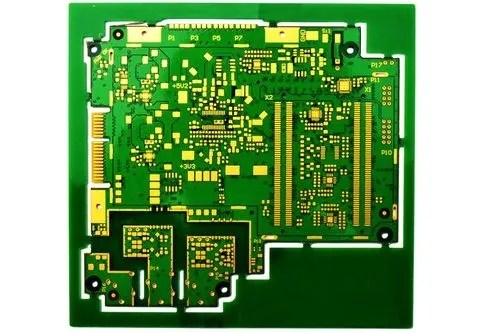

高速高密度PCB设计、电源完整性的新挑战

面对高速、高密度PCB设计的挑战,设计人员需要改变的不仅是工具,还有设计方法、理念和流程。

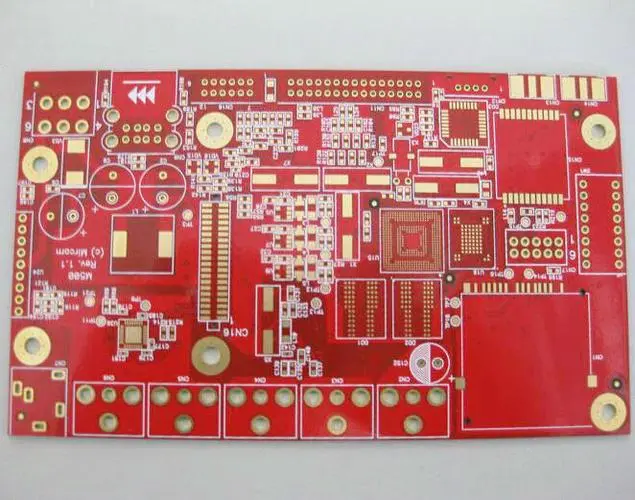

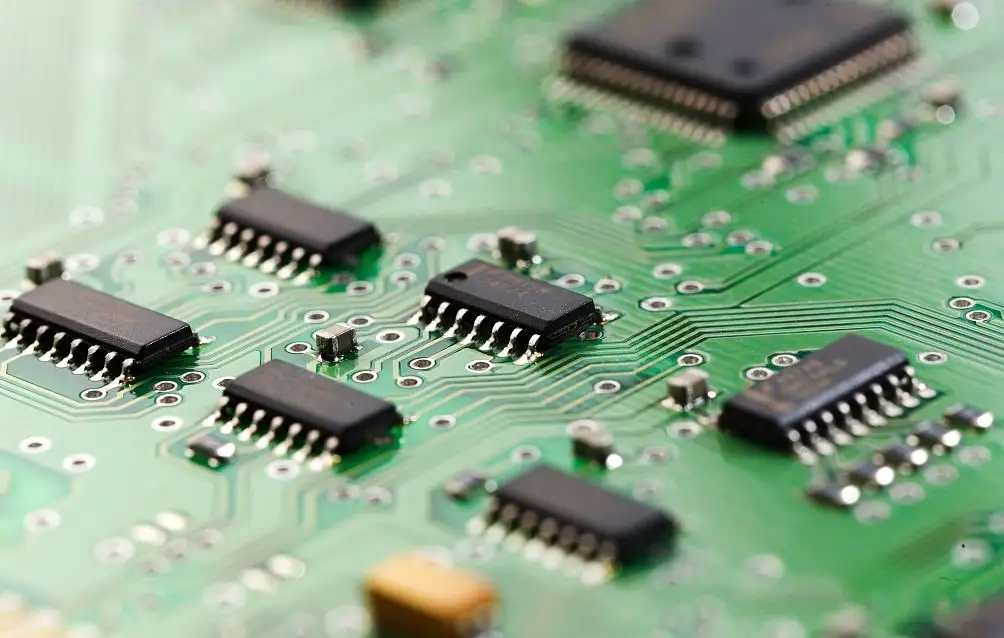

随着电子产品功能的日益复杂和性能的提高,印刷电路板的密度及其相关元件的频率不断提高,工程师面临着高速、高密度PCB设计带来的挑战 也在增加。

随着竞争的加剧,制造商在产品上市时间上面临着越来越大的压力。 如何利用先进的EDA工具和优化方法和流程,高质量、高效率地完成设计,成为系统制造商和设计工程师不得不面对的问题。

热点:从信号完整性转向电源完整性

说到高速设计,人们首先想到的是信号完整性。 信号完整性主要是指信号线上信号传输的质量。 当电路中的信号能够按要求的时序、持续时间和电压幅度到达接收芯片引脚时,电路具有良好的信号完整性。 当信号无法正常响应或信号质量无法使系统长期稳定工作时,就会出现信号完整性问题。 信号完整性主要表现在延迟、反射、串扰、定时、振荡等方面。 一般认为,当系统工作在50MHz时,会出现信号完整性问题。 随着系统和设备频率的不断增加,信号完整性问题将变得更加突出。 元器件和PCB板的参数、PCB板上元器件的布局、高速信号的布线等问题都会造成信号完整性问题,导致系统运行不稳定,甚至彻底失效。

经过几十年的发展,信号完整性技术的理论和分析方法已经比较成熟。 至于信号完整性,陈兰冰认为,信号完整性不是某人的问题。 它涉及到设计链的每一个环节。 不仅系统设计工程师、硬件工程师、PCB工程师要考虑,在制造中也不能忽视。 解决信号完整性问题必须使用先进的仿真工具,比如CADence的SPECTRAQuest,可以在设计前期进行建模和仿真,从而形成约束规则来指导后期的布局布线 并提高设计效率。 随着今年6月Cadence针对千兆赫信号的仿真器MGH的推出,这是业界首款能够在几秒内完成数万BIT千兆赫信号的仿真器,信号完整性技术得到了提升。

与信号完整性相比,电源完整性是一项相对较新的技术,被认为是高速高密度PCB设计中最大的挑战之一。 电源完整性是指在高速系统中,PDS供电系统在不同频率下具有不同的阻抗特性,使得电路板上各处的电源层与PCB上的地层之间的电压不同,导致电源不连续。 电源、电源噪声、芯片无法正常工作; 同时,由于高频辐射,电源完整性问题也会带来EMC/EMI问题。 如果电源完整性问题不能得到很好的解决,将会严重影响系统的正常运行。

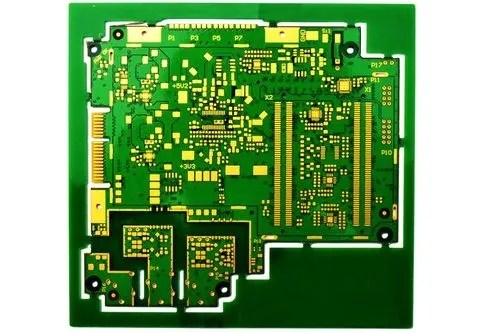

一般来说,电源完整性问题可以通过两种方式解决:优化电路板的堆叠设计和布局,以及增加去耦电容。 当系统频率小于300~400MHz时,去耦电容可以抑制频率、滤波和阻抗控制。 在适当的位置放置合适的去耦电容可以帮助减少系统电源完整性的问题。 但当系统频率较高时,去耦电容作用不大。 在这种情况下,只能通过优化电路板的层间距设计、布局布线或其他方法来降低电源和地噪声(如适当匹配以减少电源传输的反射问题)来解决电源完整性问题。 系统),同时抑制 EMC/EMI。

对于信号完整性和功率完整性的关系,陈兰冰认为:“信号完整性是时域的概念,比较容易理解,而功率完整性是频域的概念,比信号完整性更难理解,但 电源完整性在某些方面与信号完整性有相似之处,电源完整性对工程师的技能要求较高,对高速设计来说是一个新的挑战,不仅涉及板级,还涉及芯片级和封装级,建议从事高速设计的工程师 高速电路板设计应以信号完整性的解决方案为基础来解决电源的完整性。”据悉,Cadence的电源完整性工具PI已推向市场,并已成功应用于多家客户的设计中。

然后

联系

电话热线

13410863085Q Q

微信

- 邮箱