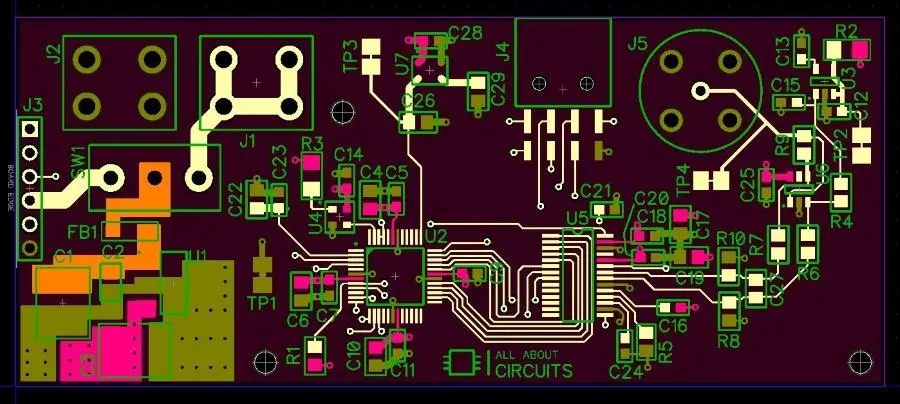

PCB设计中高速USB设计注意事项简介

设备的放置

1.、使一些时钟相关设备(例如时钟合成器、时钟缓冲器、晶体和晶体振荡器)远离高速 USB 控制器及其相关布线,并使这些时钟设备远离 I/O 端口和电源连接器。

2、晶振、晶振等器件应尽量靠近PCB表面放置。 如果有较大的接地焊盘,则应通过多个过孔将焊盘连接到 GND。

3、大电流设备尽量靠近电源放置,远离连接器,以减少大电流的回流路径,从而减少电磁辐射。

高速USB信号端接

1、如果主控制器使用了外部终端电阻,请确保终端电阻与主控制器信号输出引脚之间的距离小于 200mil。

2、EMI 测试时,有时可能会放置共模阻断器。 此时,请将其尽可能靠近连接器放置。

3、 在下游端口,确保终端电阻和 USB 连接器引脚之间有一个 15K Ohm 下拉电阻。

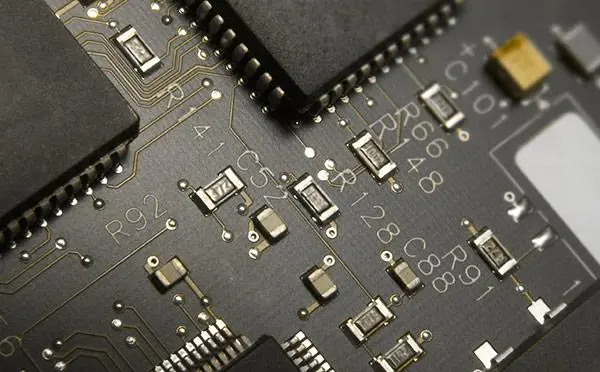

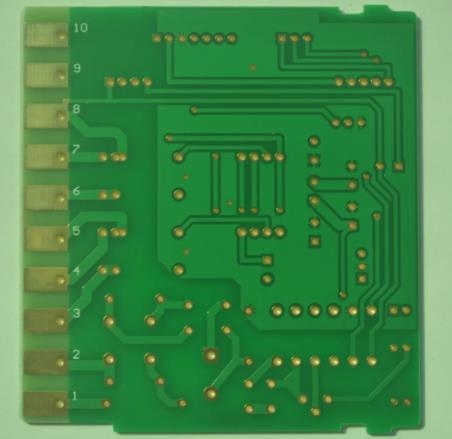

高速USB信号接线

1、 分板前放置高速USB主控制器及相关主要器件。

2、差分信号线并排走线。

3、尽可能缩短走线长度,优先考虑高速时钟信号和高速USB差分线的布线,尽量避免高速时钟信号和高速USB差分线与任何连接器接触。 接近路由。

4、不要走晶振、晶振、时钟合成器、磁性器件、时钟倍频等IC下面的信号线。

5、如果可能的话,让USB高速信号走在PCB的底层。

6、尽量减少USB高速信号线上的过孔和拐角数量,以便更好地控制阻抗,避免信号反射。

7、信号线上避免走线短,否则会引起信号的反射,从而影响信号的完整性。 如果这条短线不可避免,请确保其长度不超过 200 密耳。

8、线路敷设在一个完整的平面上(VCC或GND),现有线路的下平面没有被分割。 如果可以的话,不要跨过Anti Etch,否则自感系数和信号辐射都会增加。 同样,高速信号线也尽量同层敷设。

9、如果无法避免90度转弯,可采用两个45度实现转弯或采用弧线实现转弯,这样会大大减少信号反射和阻抗不连续性。

高速 USB 布线的间距

1、并行USB差分信号对之间的走线间距应保证差分阻抗为90欧姆。

2、根据一些仿真数据,并行高速USB差分信号线之间的最小距离控制在20mil以上,这将有助于减少高速USB差分对之间的串扰。

3、缩短并排的高速USB信号线、高速时钟线和AC信号线的长度,或增大并排之间的间距,以减少串扰的影响。 在EMI测试实验中,可靠的最小间距为50mil。

高速USB线长度匹配

1、使用高速USB信号的差分分配线时,走线的长度要匹配。 最大长度差(例如DM1和DP1之间的长度差)不能大于200密耳。

高速USB线总长度要求

1、 确保线缆到背板连接器的总长度控制在18英寸。

2、确保布线的总长度加上 USB 连接器板的电缆的总长度不超过 18 英寸。 电路板组装和电路板加工制造商解释了电路板设计的高速USB设计注意事项。

然后

联系

电话热线

13410863085Q Q

微信

- 邮箱