高速PCB设计中终端匹配电阻的放置

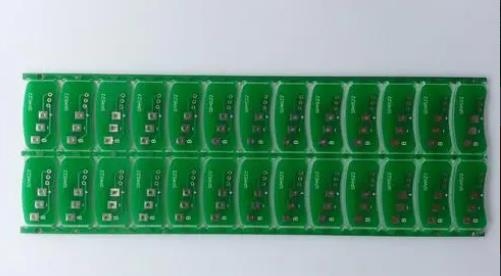

印制电路板的设计是根据电路原理图来实现电路设计者所需要的功能。 印制电路板的设计主要是指布局设计,需要考虑外部连接的布局。 内部电子元件的优化布局、金属布线和过孔的优化布局、电磁防护、散热等因素。 优秀的布局设计可以节省生产成本并实现良好的电路性能和散热。 简单的版图设计可以通过手工实现,而复杂的版图设计则需要通过计算机辅助设计(CAD)来实现。

本文简要总结了高速数字设计中串联终端匹配和并联终端匹配的优缺点,并对这两种匹配方式的终端匹配电阻处于不同位置时的匹配效果做了相应的仿真和深入分析。 。 结论是串联终端匹配电阻的位置要求不如终端匹配电阻严格,并对终端匹配电阻的放置提出了一些建议。 它为如何在 PCB 设计中放置终端匹配电阻提供理论和实践指导。

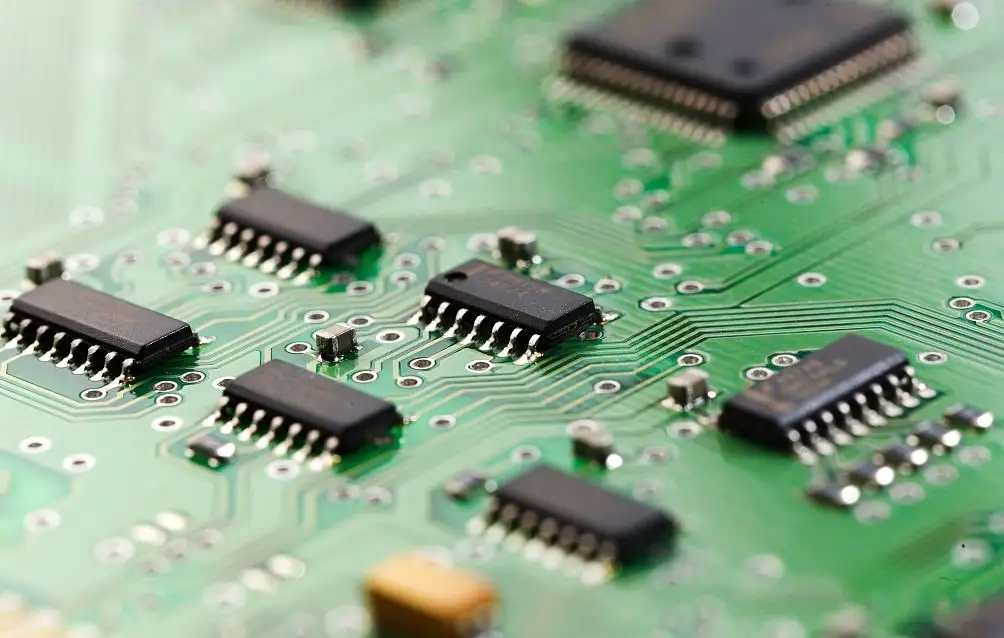

随着半导体技术的快速发展,信号上升时间越来越短,导致信号完整性问题日益突出; 另外,器件小型化的趋势越来越明显,电路板的面积也变得越来越小,因此对PCB的布局要求也越来越严格。 这就需要高速PCB设计工程师严格考虑各种器件的放置,包括滤波电容、匹配电阻等,以提高系统的信号完整性,同时节省PCB面积。 对简单的并联端匹配和串联端匹配进行仿真分析,研究不同位置匹配电阻对信号质量的影响。

并联端子匹配与串联端子匹配的优缺点

在高速数字设计中,经常使用电阻来匹配传输线的阻抗,以消除传输线上的反射。 有两种典型且简单的匹配方法:简单的并联端子匹配和串联端子匹配。 简单并联端的匹配电阻与输入阻抗极高的接收端并联,并接地或供电,以消除接收端的反射。 优点和缺点是匹配电阻的阻值可以精确选择,但会消耗直流功耗。 源端串联匹配电阻,与输出阻抗较小的驱动器串联,吸收接收端反射的信号。 这种方法的优点和缺点是不消耗电力。 然而,由于许多驱动器是非线性的,例如TTL器件,其输出阻抗随着器件逻辑状态的变化而变化,这使得匹配电阻的阻值很难确定。 因此,在要求低功耗的数字设计中,更常用的是串行端子匹配方式; 并行端匹配方式更多地应用于模拟电路设计中,以牺牲功耗为代价来满足其高精度要求。 本文将总结串联端子匹配模式的另一个优点,即PCB中匹配电阻对位置的要求比简单的并联端子匹配模式不那么严格。 PCB加工和PCBA加工厂家将讲解串行端子匹配和并行端子匹配在高速数字设计中的优缺点。

然后

联系

电话热线

13410863085Q Q

微信

- 邮箱