PCB 设计:是否应该在 PCB 电源层中布线信号?

再次,我们有一个很好的例子,即长期存在的 PCB 设计指南没有足够的背景。 这个问题的简短回答是“是”,在某些情况下可以这样做。 这是一种常见的做法。 我们在客户板上执行此操作。 这些产品不存在任何阻抗问题、EMC问题或直流功率损耗,因为堆叠设计是正确的,并且因为我们已经考虑了如何正确接线设计。 然而,当在电源层上布线信号或在信号层上布线时,需要考虑多个维度。 考虑电路板中的电源完整性、受控阻抗和直流电源分布会产生困难。

如何在 PCB 电源平面层中路由信号

在开始切割 PCB 的电源平面层和布线之前,需要考虑以下设计要求:

电源层电流容量。

低速和高速信号和阻抗。

如果使用平面作为参考图层,则返回路径让我们更详细地了解每个区域。

电源层电流容量。

每当您设计电源层时,它都会有一些定义的载流能力,这与构成平面层的铜的尺寸有关。 如果通过高功率平面开始布线,则会将该平面分成多个部分,并且每个部分的电流容量将低于统一平面层。 此外,如果电源层的形状非常复杂,您最终可能会创建一个具有高电流密度的漏斗,该漏斗会变得非常热。 您可以在 PDN 分析器模拟中可视化这种效果。

高电流电源层中的该区域可以充当具有较低电流容量的阻断点。

补偿电源层布线的一种解决方案是使用在相邻层上并行运行的另一个电源层。 在这种布置中,您实际上将电流分流到两个平行平面,这将有助于确保您不会超过平面任何部分的电流容量。 对于大多数低功耗设备,您通常不需要担心这一点。 但是,如果您有一个高功率系统,您可能无论如何都需要这样做,以便系统可以提供足够的功率而不会变得太热。 常见的示例是背板 (3U/6U) 或其他机架安装单元。

跟踪阻抗

如果您没有将控制阻抗线穿过电源层的覆铜布,则不必太担心。 只要您遵循此列表中的其他准则(如果适用),低速数字协议(例如 SPI 和 I2C 以及 GPIO)就可以通过铜涂层进行路由,而不会出现任何问题。 阻抗很重要的高速协议是另一回事,您需要确保这些走线周围有足够的覆铜间隙,以确保不违反阻抗目标。 如果您的功率注入距离布线太近,则需要在层堆栈中使用共面计算,以确保不违反阻抗容差。

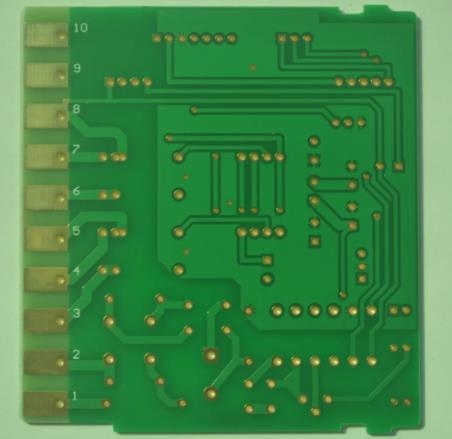

在这个例子中,我已经清除了电源层,因为在这一层中更容易为布线腾出空间。 请注意,我还忽略了大中心区域的铜,因为由于电路板的常规间隙,它没有提供任何有用的功能。

通过应用高间隙来切割平面所涉及的危险是铜最终会被切割成太多的部分。 如果走线过多,布局周围会留下大量残铜,铜会被切成小片。 对于也需要阻抗控制的低层板,您可能没有另一个电源层来重新连接所有这些部件。 如果您发现必须通过电源层布线很多电线,最好再添加两层(电源层和接地层)。

返回路径

与任何其他情况下的布线一样,请确保 PCB 中的信号具有明确定义的返回路径,尤其是在电源层布线时。 这里的问题是如果您在相邻层中布线。 当您在与电源区域相同的层中布线时,您将在参考平面中放置间隙。 对于功率区域,这通常没问题,除非您使用功率区域作为另一层信号的参考。 然后,如果您碰巧穿过这些间隙之一,则会创建一个寄生电感较高的区域,然后会从串扰或外部源接收到更多的 EMI。

对于在两个平面层之间传播的低速协议,只要另一层的平面是统一的,就可以通过分离电源平面进行路由。 您创建的阻抗不连续性将是电气短路,因此您不必担心反射,并且另一层上的平面的存在有助于确保仍然存在清晰的返回路径,即使该区域的电感很高 当飞机分裂时。 对于更高速度的信号,这一点更为重要。 你最好添加一个新层来为这些信号腾出空间,而不是切断电源层。

概括

总之,如果您使用不需要阻抗控制的低速数字信号进行操作,我不会太担心覆铜电源中的接线。 请注意电源层周围的电流路径,尽量不要将电源层切割成孤岛。 在其他情况下,您应该使用额外的层并将它们路由到那里。 另外,必要时请注意阻抗要求:铜箔距离带状线或微带线太近会导致阻抗偏差,确保附近有另一个参考平面,并避免通过相邻层的间隙布线。

---- PCB 组装和 PCB 加工制造商解释: PCB 设计:是否应该在 PCB 电源层中布线信号?

然后

联系

电话热线

13410863085Q Q

微信

- 邮箱