工程师对高速PCB设计有何解释?

大多数 PCB 都被认为存在某种类型的信号完整性问题的风险,这些问题通常与高速数字设计相关。 高速 PCB 设计和布局侧重于创建不易受到信号完整性、电源完整性和 EMI/EMC 问题影响的电路板设计。 尽管没有任何设计能够完全避免这些问题,但这些问题可以减少到微不足道的程度,并且不会在最终产品中造成性能问题。

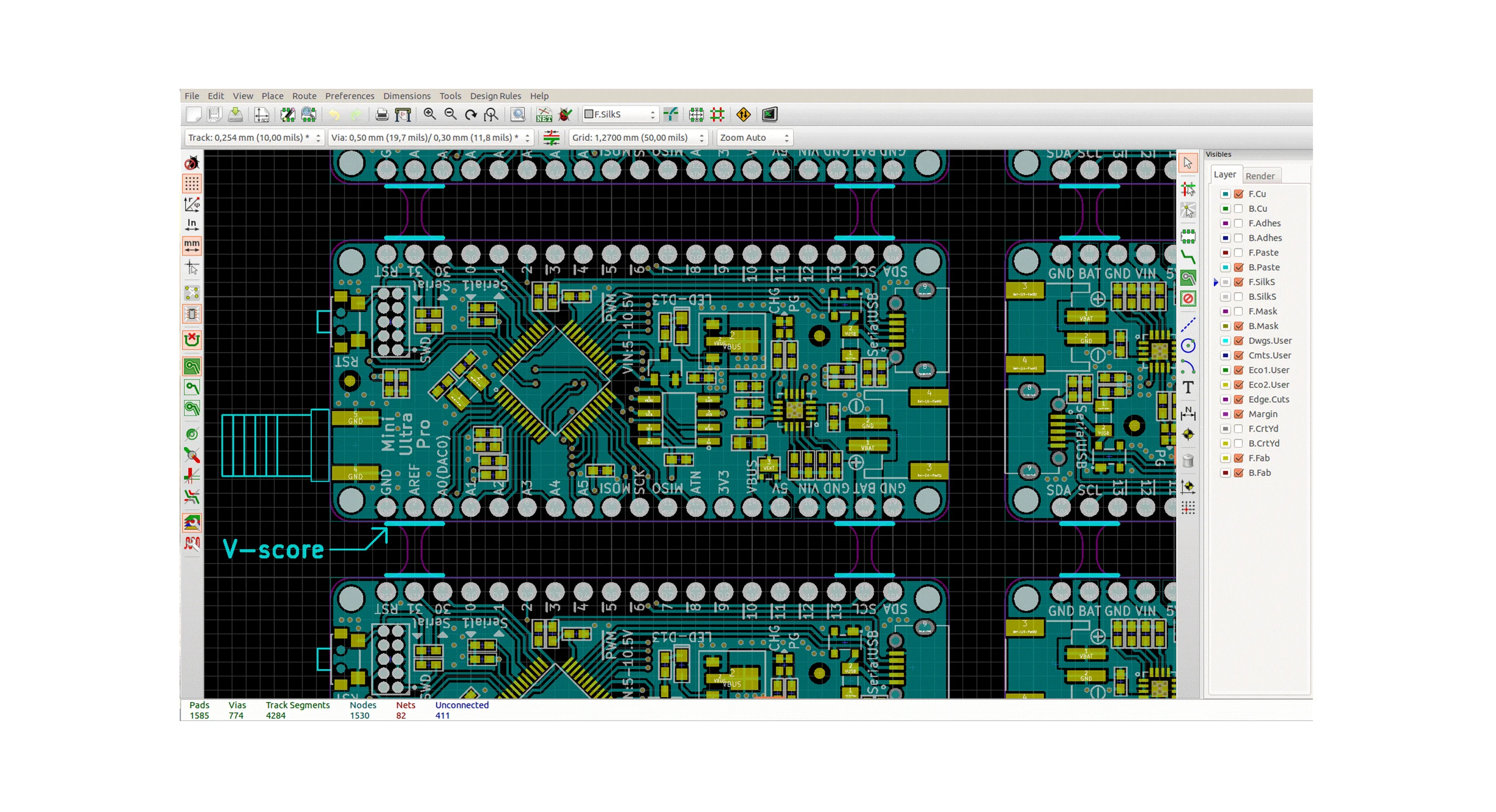

创建原理图并准备过渡到电路板布局后,您需要使用 PCB 设计工具中的特定功能来进行正确的布局和布线。 在 PCB 设计软件中,您将有机会在层堆叠中准备电源和接地平面布局、计算布线的阻抗分布以及查看堆叠 PCB 材料选项。 高速设计的大多数方面都围绕 PCB 堆栈设计和布线,以确保信号和电源完整性,而正确的 ECAD 软件可以帮助确保在这些领域取得成功。

高速设计是指使用高速数字信号在组件之间传输数据的系统。 高速数字设计和具有较慢数字协议的简单电路板之间的分界线并不明确。 将特定系统表示为“高速”的一般指标是系统中使用的数字信号的边沿速率(或上升时间)。 大多数数字设计同时使用高速(快边沿速率)和低速(慢边沿速率)数字协议。 在当今嵌入式计算和物联网时代,大多数高速 PCB 都具有用于无线通信和网络的 RF 前端。

虽然所有设计都是从原理图开始,但高速PCB设计的主要部分集中在互连设计、PCB堆叠设计和布线上。 如果您在前两个领域取得成功,那么您很可能在第三个领域取得成功。 阅读以下部分,了解如何开始高速设计以及 PCB 设计软件的重要作用。

规划 PCB 堆叠和阻抗

您为高速电路板创建的 PCB 堆栈将决定阻抗和接线的难易程度。 所有 PCB 层均包含一组专用于高速信号、电源和接地层的层。 在层内分配层时需要考虑以下几点:

电路板尺寸和网络数量:电路板有多大以及在PCB布局中需要布线多少个网络。 物理尺寸较大的电路板可能有足够的空间让您在整个 PCB 布局中进行布线,而无需使用多个信号层。

布线密度:当网络较多且电路板尺寸仅限于较小区域时,您可能没有足够的空间在表层周围布线。 因此,当布线更近时,您将需要更多的内部信号层。 转到较小的一个

接口数量:有时,根据总线的宽度(串行和并行)和电路板的尺寸,每层上仅布线一个或两个接口是一个很好的策略。 将高速数字接口中的所有信号保持在同一层,以确保所有信号都能看到一致的阻抗和偏转。

低速和射频信号:您的数字设计中是否有低速数字或射频信号? 如果是这样,它们可能会占用可用于高速总线或组件的表面空间,并且可能需要额外的内层。

电源完整性:电源完整性的基石之一是针对大型 IC 所需的每个电压级别使用大型电源层和接地层。 它们应放置在相邻层上,以帮助确保高平面电容,以通过去耦电容器支持稳定的电源。

PCB 材料选择、层数和厚度

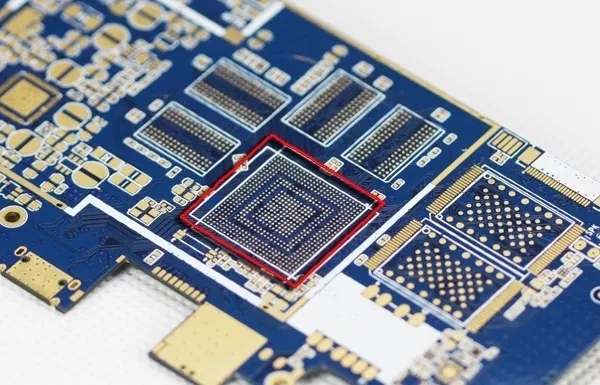

在设计 PCB 堆栈之前,请考虑容纳设计中所有数字信号所需的层数。 有很多方法可以确定这一点,但这些方法取决于一些数学计算和一些过去高速电路板设计的经验。 除了上面列出的考虑层数的要点之外,具有 BGA/LGA 封装的大型高速 IC 还可以确定所需的电路板尺寸。 进行BGA扇出时,每个信号层一般可以放置2根线,并保证在搭建堆叠时将电源层和接地层包含在层数中。

FPGA 上的 BGA 扇出具有大多边形,用于高速设计中的供电。

FR4级材料通常可用于高速数字设计,只要元件之间的路线不太长。 如果路由确实变得太长,您的高速通道中将会出现太多损耗,并且通道接收端的组件可能无法恢复信号。 选择材料时要考虑的主要材料特性是PCB层压板的损耗角正切。 通道几何形状也将决定损耗,但具有较低损耗角正切的 FR4 层压板通常是较小电路板的良好起点。

如果您的线路太长,您可能需要更专业的材料作为高速信号的基材。 基于 PTFE 的层压板、分散玻璃层压板或其他特殊材料系统非常适合支持大型高速数字板,其中布线较长且需要低插入损耗。 用于小型高速 PCB 的入门级高 Tg 层压材料的良好组合是 370HR。 对于较大的电路板,Megtron 或 Duroid 层压板是不错的选择。 在继续之前,请咨询您的制造商,以确保您选择的材料和推荐的叠片是可制造的。

阻抗控制

只有在创建推荐的堆栈并与制造商验证后才能确定阻抗。 制造商可能会建议对 PCB 堆栈进行修改,例如替代 PCB 材料选项或层厚度。 一旦您获得了要使用的层的许可并最终确定了层的厚度,您就可以开始计算阻抗值。

阻抗通常使用公式或计算器以及场求解器工具来计算。 设计中所需的阻抗将决定传输线的尺寸以及与附近电源或接地层的距离。 以下工具可用于确定传输线宽度:

IPC-2141 和 Waddell 的公式:这些公式提供了阻抗估计的起点,并且它们在较低频率下产生准确的结果。

2D/3D 场求解器实用程序:场求解器用于求解您为高速板定义的传输线几何形状中的麦克斯韦方程。

将层堆栈管理器与场解算器结合使用将为您提供最准确的结果,同时考虑铜粗糙度、蚀刻、不对称线对准和差分对。 计算出线路的阻抗曲线后,需要在布线工具中将其设置为设计规则,以确保线路具有所需的阻抗。

高速板传输线设计的阻抗计算。 Altium designer 中的层堆栈管理器包含一个用于计算铜粗糙度的阻抗计算器。

大多数高速信号协议(例如PCIe或以太网)都使用差分对布线,因此需要通过计算布线宽度和间距来设计特定的差分阻抗。 场求解器工具是计算任何几何形状(微带线、带状线或共面)的差分阻抗的最佳工具。 场解算器实用程序的另一个重要结果是传播延迟,它用于在高速布线期间强制进行长度调整。

高速PCB布局规划

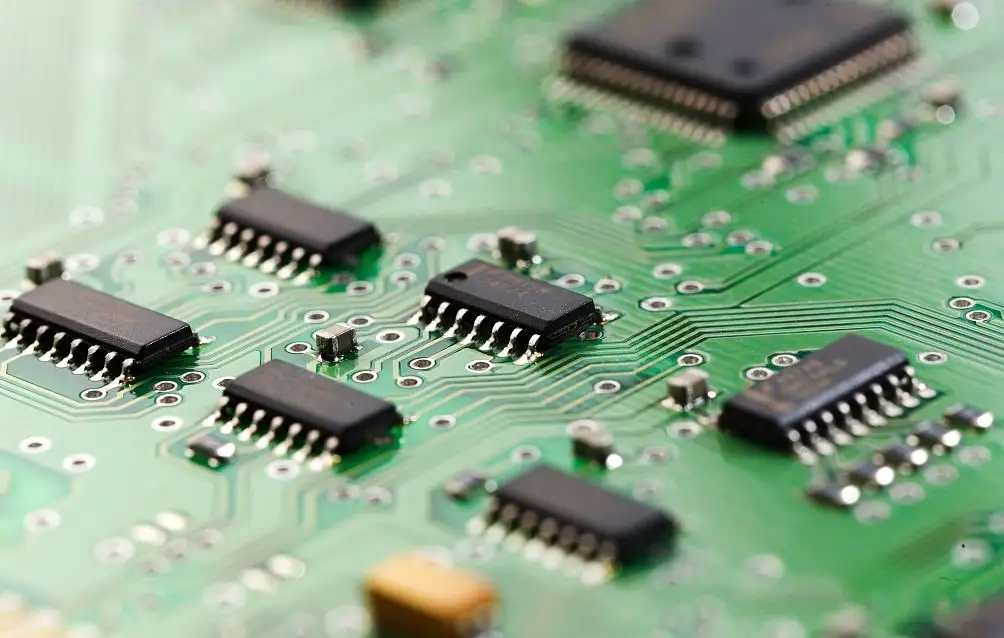

对于高速 PCB 布局中元件的放置位置,没有具体的规则或标准。 一般来说,将最大的CPU IC放置在电路板中心附近是一个好主意,因为它通常需要以某种方式连接到电路板上的所有其他组件。 直接连接到中央处理器的较小的 IC 可以放置在中央 IC 周围,以便组件之间的布线可以保持短而直接。 然后可以将外围设备放置在电路板周围以提供所需的功能。

当主控制器IC放置在电路板中心附近,而其他高速外设放置在其周围时,高速布局是最佳的。 这也是主板将大型处理器放置在主板中央的原因之一。 Altium Designer 中的 MiniPC 项目将其 PCIe、DDR4、USB 3.0 和以太网外设放置在中央 FPGA SoC 周围,因此布线更加容易。

放置元件后,您可以设置设计工具来帮助您开始设计布线。 这是高速电路板设计的敏感部分,因为不正确的接线会损害信号完整性。 然而,如果前面的步骤正确完成,则更容易实现信号完整性。 您应该在 PCB 设计规则中设置阻抗曲线,以便设计中的任何布线都以正确的宽度、间隙和间距放置,以在布线过程中保持受控的阻抗。

然后

联系

电话热线

13410863085Q Q

微信

- 邮箱